Kactus2 is a graphical open source IP-XACT toolset that will make the design process of embedded systems easier even for a novice engineer. It is growing into an open reference for benchmarking other metadata-based tools

Anagha P.

Kactus2 is metadata-based software for sketching, packing, integrating and generating both hardware and software for embedded products at several hierarchy levels. It is the first graphical open source design environment that is IEEE1685/IP-XACT compatible, and is used to design embedded multiprocessor system-on-chip (MPSoC) products. It enables easier reuse of IP and practical hardware/software abstraction for smooth development of application software, thereby increasing productivity. This software is created by assembling application-specific components on general-purpose platforms, and the components are packetised to a metadata library. The use of metadata ensures less error-prone design.

Developed by Tampere University of Technology (Finland) for its Funbase project, Kactus2 gives an easy start to metadata-based designs even without prior expertise. It makes field programmable gate arrays (FPGAs) easy for software engineers and provides hardware abstraction for programmers with the use of multicore communication application programming interfaces (MCAPIs). Kactus2 comes with an intuitive user interface. It is also equipped with built-in generators for top VHDL, Modelsim and Altera Quartus projects. Kactus2 is mostly written in C++ and has a young but well-established codebase.

Who will benefit from Kactus2?

Kactus2 is ideal for small- and mid-sized vendors and integrators who currently have only the conventional software like Office (Doc, Excel, PowerPoint, etc) for specifications/documentation and VHDL, C/C++ and FPGA tools for designs. It helps easily start a metadata-based design, increasing the manageability of the product while still using the conventional tools mentioned earlier.

The software is useful for universities and research laboratories that implement new content (IP blocks, software modules, etc). Kactus2 helps packetise the content in a standard way, thus enabling the use and reuse of data by others, particularly when the original contributor leaves, for instance, after a PhD project.

Kactus2 offers a great R&D environment for bigger companies and tool providers that already have modern design tool flows and resources for developing higher abstraction methods. It offers a platform for trying new methodologies and user interface innovations.

Features

Kactus2 helps the user create quick drafts of block diagram blueprints for printed circuit board (PCB), integrated chip (IC), SoC and IP, and store the files in the IP-XACT format. It can draft Multicore Association’s MCAPI endpoints and channel designs for all processors and fixed IPs in a product. It also generates code templates (VHDL entities and headers) for new IP blocks from descriptions of IP-XACT components.

This software creates electronic datasheets of your existing IPs, which are stored in the library as templates and blocks, ready for integration. It imports and integrity-checks IP libraries from any standard compatible IP vendor and exports your IP library. These features facilitate the reuse and exchange of IPs.

Kactus2 aids in the creation of hardware designs with hierarchy, software architecture in MCAPI communication abstraction and system designs that map software to hardware. It configures all designs, i.e., it sets the requirements, constraints, optimisation, active views, etc. This tool generates structural top-level VHDL and performs software builds for all processors. It also creates combined documentation from all blocks, through all hierarchy levels.

However, Kactus2 cannot create IP functionality. HDL editors and integrated development environment (IDE) software should be used for that. TCE tools may also be used to create C-to-VHDL so that IP can be created from C source without knowing any HDL. Another drawback is that it doesn’t allow the generation of binary and executable files either. Additional HDL synthesis and software compilation tools should be used for this purpose.

System requirements

Operating system: Linux, Windows 7, Windows Vista or Windows XP.

Installation

The installation is simple and takes only minutes. Download the *.exe file that your OS supports. Double clicking on it opens the installation window. Go through the procedure to install Kactus2 on your computer.

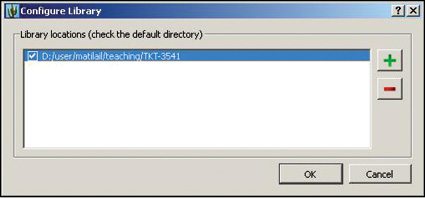

Configure library paths

Clicking on the Configure library icon from the Library in the top pane opens a dialogue box. Browse and add the location where you downloaded the library from opencores.org to make sure that you can access the files created from different computers. This should be set every time Kactus2 is accessed from a different computer.

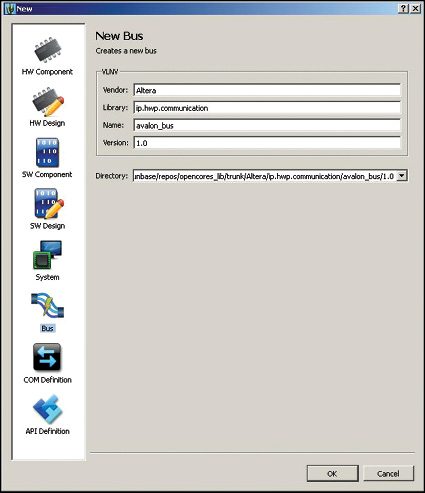

Create a bus

The bus is pre-given in the exercise library.

To create a new bus, go to File, select New, and in the new window that appears, select Bus from the left hand menu. On the right side will be several VLNV fields, as shown in Fig. 2.