Are you working on a new electronics project from scratch? Does it include a designing-and-automating process? Do you have all the required electronics design and automation (EDA) tools for the same? I understand that such projects need a lot of designing tools, and it is tough to find all EDA tools separately and then install these one by one on Windows. So, if you are well-versed with Fedora operating system (OS) and are using one, the solution to all your problems would be Fedora Electronic Laboratory (FEL).

FEL is a spin on Fedora that contains all software one would require for EDA. It provides all the different open source hardware design flows depending on the semiconductor industry’s current trends.

FEL is a spin on Fedora that contains all software one would require for EDA. It provides all the different open source hardware design flows depending on the semiconductor industry’s current trends.

Reason for existence

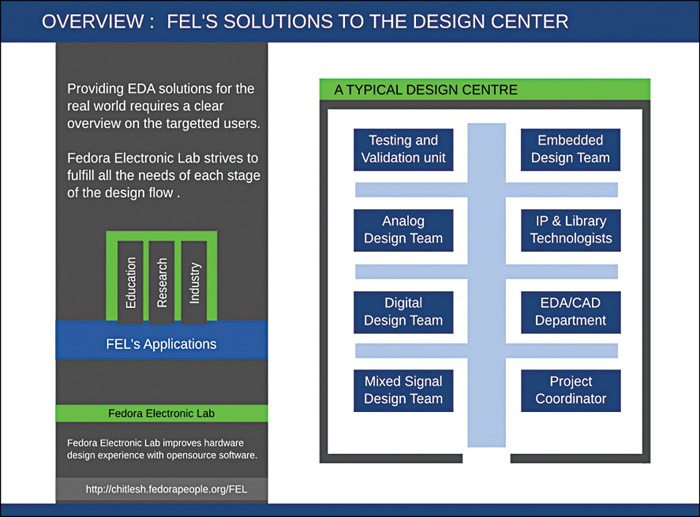

The usual problem that designers have at hand is that they do not find any open source EDA solution for a real-life problem. Now, while engineers use EDA software to design chips or circuit boards, it requires a set of hardware design tools to design chips. However, the same set of hardware design tools need not work with every hardware design project. Although FEL is limited to Fedora OS, it could make its existence possible only because it had the solution to all problems discussed above.

The open source EDA software included in FEL meets the demands of field-proven problems. This open source platform helps you keep in pace with the current technological race with open source community support. This community helps users with installation and use of any EDA tool in the spin.

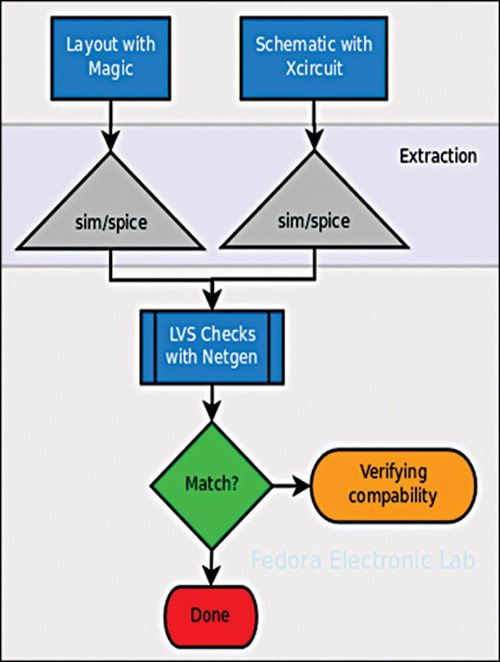

FEL as a platform has the ability to map the three methodologies—design, simulation and verification. These methodologies enable one to have a better hardware design flow and experience. These also help Fedora achieve its aim to support innovation and development brought by the open source community.

Collaborative hardware review

Collaborative hardware review

The digital hardware design has many requirements, one of which is to track files and feed these into multiple EDA tools. Then, reports and netlists have to be analysed carefully and logged-in further. All of these are tracked by the companies under project dependent files. Fedora makes all of these processes easy through a dedicated web server, meant especially for hardware design and code reviews through FEL. It also helps improve their sign-off methodologies.

Designers are often confused about hardware code reviews, and inexperienced companies are often misguided due to which plenty of time is wasted. Moreover, code-sharing takes place in an inefficient way (in a non-acceptable format) due to which misunderstandings arise. This web server solves all these issues, collaborating all hardware tools and their files.