This technology features the highest number of vertically stacked transistors to date, promising significant improvements in electronic performance and efficiency.

Transistors, essential for amplifying and switching electrical signals in many electronic devices, are continually being improved in performance, energy efficiency, and size. Researchers at King Abdullah University of Science and Technology (KAUST) have recently advanced this field by developing three-dimensional (3D) integrated transistors that can be vertically stacked. Their design has the highest number of stacked transistors to date, potentially boosting electronics’ performance significantly. As technology progresses, the demand for more powerful, efficient, and compact electronic devices increases. Conventional planar transistors, however, are hitting physical and performance barriers, contributing to the deceleration of Moore’s law.

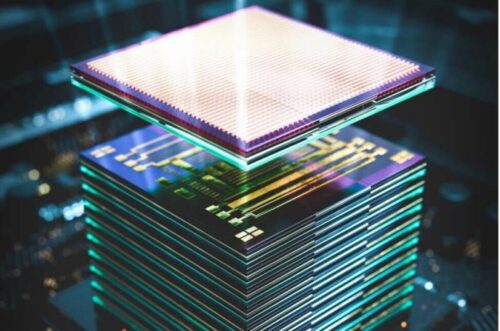

To tackle these challenges, the team explored approaches beyond the two-dimensional layout of traditional transistors. Their research focused on vertical stacking, allowing transistors to be layered on top of each other, increasing transistor density and improving electronic performance. They mentioned that their goal was to increase transistor density. They have developed a 10-stack nanometer-thick compound semiconductor transistor with a low thermal budget and low interfacial roughness, maximizing wafer space utilization. This vertical stacking significantly enhances processing power and efficiency. The design includes ten layers of indium oxide (In2O3) thin-film transistors (TFTs) on CMOS-compatible silicon/silicon dioxide (Si/SiO2) substrates, maximizing wafer space and achieving greater transistor density compared to planar designs. Each layer functions independently but contributes to overall performance. Indium oxide was chosen for its excellent electrical properties, and parylene-C for its effective insulation and room temperature processing compatibility.

Fabrication involved depositing a thin layer of In2O3 on a silicon wafer, forming the channel for electrical current, followed by a layer of parylene-C as the dielectric. An advanced, 72-step lithography-based process was used to pattern each layer, ensuring precise alignment and performance. Initial tests showed remarkable electronic performance, with a maximum field-effect mobility of 15 cm²/V·s, a subthreshold slope of 0.4 V/dec, and a current on/off ratio up to 10⁸, surpassing many existing thin-film transistors. These transistors demonstrated faster switching speeds, lower power consumption, and improved overall performance. The team highlighted the potential applications of this technology in various fields, including mobile devices, IoT, AI, machine learning, consumer electronics, and automotive electronics. Future research will focus on scaling transistors down to the nanoscale, exploring new techniques to reduce power consumption, and enhancing reliability and stability for broader deployment.

“Our paper showcases the world’s largest number of stacked metal oxide transistors, addressing the limitations of traditional planar transistors,” explained Xiaohang Li, co-author of the study.