A digital counter whose logical output increments in steps on receiving clock pulses is used for a variety of counting and timing applications. It is at the heart of digital clock circuitry and other similar timing devices.

A digital counter whose logical output increments in steps on receiving clock pulses is used for a variety of counting and timing applications. It is at the heart of digital clock circuitry and other similar timing devices.

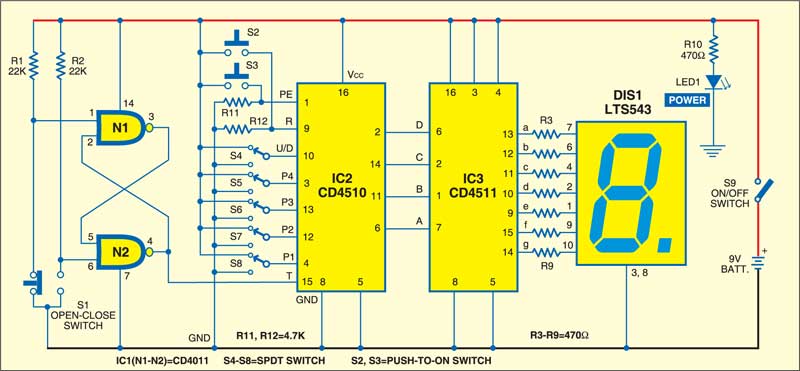

Digital counter circuit

The counter comprises two NAND gates of CD4011, up/down counter CD4510, 7-segment decoder CD4511 and some discrete components. NAND gates N1 and N2 are configured in the form of a flip-flop. When switch S1 is pressed, pin 4 of gate N2 goes high and generates a low-to-high clock pulse for counter CD4510. This clock pulse is counted by CD4511 and displayed on 7-segment display DIS1. IC CD4511 (IC3) is used to decode the data for the 7-segment display.

Pins 1 and 9 of IC2 are pulled down with resistors R11 and R12, then connected with switches S3 and S2, respectively. Switches S2 and S3 are used for reset and parallel data loading, respectively. If pin 10 of IC2 is high, the counter will be in ‘up’ mode.

Circuit operation

Momentarily press micro-switch S1 once, thus sending one clock pulse. The display shows ‘1.’ Continue pressing and releasing switch S1 and you will notice that each clock pulse increments the 7-segment display by one digit. Continue this exercise until the display shows ‘9.’ The next press-and-release operation will change the display to ‘0,’ indicating that the counter has been reset and that it has completed its one cycle.

Now change the position of switch S4 to GND. Give a clock pulse from switch S1. The display will show ‘9’. This indicates that the counter has now started counting downwards. Reverse counting is justified as we have already selected the down-count mode.

For parallel data loading, first set the parallel data by switches S5 through S8 (either GND or Vcc) and then press switch S3. The set parallel data appears on the 7-segment display. Let us assume that parallel down-count data (maximum) is ‘0101.’ You will observe that the display changes to ‘5’ after switch S3 is pressed. LED1 acts as the power indicator.

The article was first published in December 2006 and has recently been updated.