- Enables engineers to overcome DFE analysis challenges with automation, quick and efficient validation and debugging of DDR5 designs

- Also allows proficiency in de-embedding of DDR5

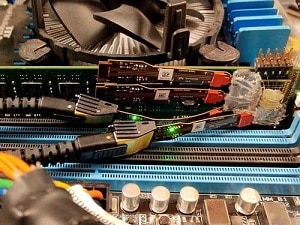

5G is driving rapid growth in a variety of emerging technologies – from augmented reality and artificial intelligence to cloud computing and IoT – making DDR5 more important than ever. Rapid access to high volumes of stored data means complex designs are pushing boundaries of signal integrity, requiring higher performance measurements for compliance, debugging and validation.

5G is driving rapid growth in a variety of emerging technologies – from augmented reality and artificial intelligence to cloud computing and IoT – making DDR5 more important than ever. Rapid access to high volumes of stored data means complex designs are pushing boundaries of signal integrity, requiring higher performance measurements for compliance, debugging and validation.

Therefore, Tektronix, Inc. has launched the new TekExpress DDR5 Transmitter Solution which allows engineers to overcome DFE analysis challenges with improved automation, quick and efficient validation and debugging of DDR5 designs to meet more than 50 electrical and timing measurements as defined in JEDEC and master DDR5 de-embedding techniques with Serial Data Link Analysis (SDLA).

Automated measurement

The tools used for debugging DDR3/4 are insufficient when testing DDR5 designs in the presence of inter-symbol interference (ISI). Tektronix’ DDR5 system level compliance software provides a variety of automated tools to overcome the challenges that come with the next generation of DDR including:

- Rx DFE Equalization support for the write data eye measurement on DDR5 traffic

- Automated measurement for 50+ DDR5 electrical and timing parameters as defined in JEDEC

- New algorithms to consistently and reliably differentiate between read and write bursts

- New compliance application architecture with enhanced automation to reduce test time and help bring designs to market faster.

Provides full control

The TekExpress DDR5 Transmitter Solution puts control back in the hands of the engineer with a user defined acquisition mode which runs DDR5 JEDEC compliance measurements by customizing scope settings including sample rate, record length, bandwidth and more.

Tektronix’ standalone DDR5 DFE application provides total control over the DFE Gain and 4 tap values allowing engineers to run internal test plans, perform simulation of measurement correlation to fine tune simulation models and conduct what-if analysis by changing 4-tap and gain values.

Enhanced validation

Validating s-parameters is often the primary concern when de-embedding DDR5 designs. With improved passivity checking, port assignments and plotting capabilities, Serial Data Link Analysis (SDLA) enhances s-parameter file validation, improves flexibility and increases confidence in the de-embedding process while saving time. Other debug software tools require users to complete the entire process to find results. The TekExpress DDR5 Transmitter Solution allows users to detect problems earlier and allows more efficient debugging and optimization of designs.

The Tektronix TekExpress DDR5 Transmitter Solution is available now worldwide.