RISC-V CPU boasts 3.27 CoreMark/MHz performance with M,A,C and B RISC-V ISA extensions.

Semiconductor company, Renesas Electronics Corporation, has announced the development and testing of a new 32-bit CPU core based on the open-standard RISC-V instruction set architecture (ISA). The new RISC-V (Reduced Instruction Set Computer) CPU core will complement Renesas’ existing 32-bit microcontrollers (MCUs) portfolio, which includes the proprietary RX Family and the RA Family based on the Arm Cortex-M architecture.

The central processing unit (CPU) can function as a main application controller, a secondary core in system-on-chips (SoCs), on-chip subsystems, or in deeply embedded ASSPs (Application-specific standard product). The RISC-V CPU boasts 3.27 CoreMark/MHz performance, surpassing similar architectures. Its efficient silicon area implementation reduces operating and standby leakage currents, lowering costs.

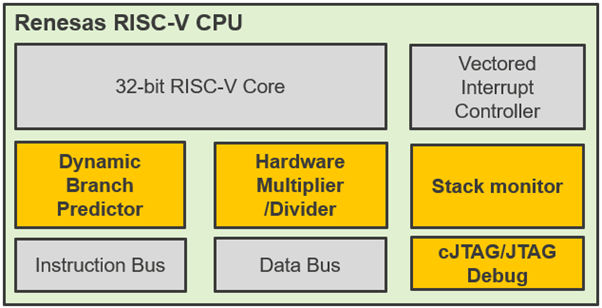

The CPU can be optimized using the RV32 ‘I’ or ‘E’ option, depending on the application’s needs. Renesas has integrated several RISC-V ISA extensions, including the M extension for optimized multiplication and division operations, the A extension for atomic access instructions, the C extension for compressed instructions to save memory space, and the B extension for bit manipulation.

The RISC-V ISA allows designers to choose elements based on their use case, optimizing power consumption, performance, and silicon footprint. A stack monitor register is added to detect and prevent stack memory overflows, enhancing application software robustness.

The CPU features a dynamic branch prediction unit for efficient code execution and supports compact Jtag debug interfaces, suitable for microcontrollers with limited pins. Its architecture includes a register bank save function to improve response latency and enable real-time behavior in embedded devices. An instruction tracing unit is available for deeper insight into system behavior.

Renesas has previously introduced 32-bit voice-control and motor-control ASSP devices and the RZ/Five 64-bit general-purpose microprocessors (MPUs) based on CPU cores developed by Andes Technology Corp. Renesas is currently sampling devices based on the new core to select customers and plans to launch its first RISC-V-based MCU and development tools in Q1 2024.