The HLS of Xilinx Vivado design suite allows the user to write programs for ASICs and FPGAs in C and C++ languages, and easily convert these to hardware description languages (HDLs). So, even software engineers can now design with FPGAs. This is a big productivity boost for customers, as many people know C and C++ but not HDL, VHDL and Verilog. Software tools, like software-defined specification environment for networking (SDNet) and SDAccel by Xilinx, are software development environments for FPGAs and/or SoCs. These tools help in better hardware and software partitioning and improve design integrity.

The DesignInsight technology by Tabula, which consists of architecture, chip design and Stylus compiler software, allows real-time observation, debugging and validation of individual logic cells of PLD in real-time (up to 2GHz).

Application and industry specific

FPGAs are programmable for all industries. But there are several stringent certification procedures and requirements to approve a device for certain applications, like military, automotive and medical. Due to this reason major FPGA manufacturers are now introducing FPGAs specific to certain fields of applications. These are becoming more ASIC-like. For example, Altera Enpirion PowerSoCs and Cyclone V SoC FPGAs are automotive grade, Altera Arria 10 FPGAs and SoCs are fully-compliant with military standards, and Kintex Ultrascale is suited for data centres, video and medical imaging, broadcast systems and radars.

Data centre acceleration. Apart from working closely with CPUs and improving response time, throughput and efficiency, FPGAs these days also make programming and debugging easy by letting designers work in languages and architectures they are familiar with, such as MATLAB/Simulink, OpenCL, ARM DS-5 and HLS. This is a major advantage to data centre programmers.

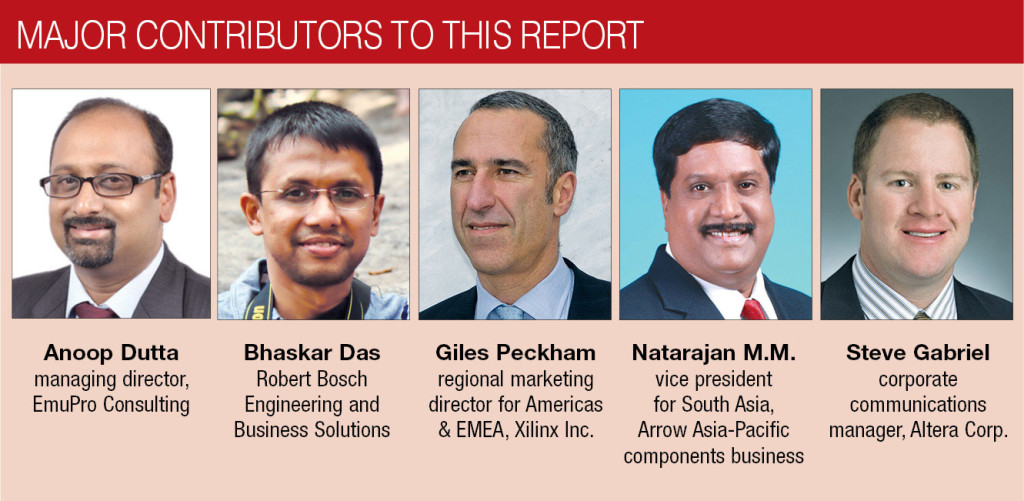

Network enrichment. The IoT environment is varied and uncertain, mentions Steve Gabriel, corporate communications manager at Altera Corp. The fast, computationally efficient programmable chips are suitable for the IoT segment in terms of power efficiency, time sensitivity and security. These are effective for IoT hubs that have to support a large number of ultra-low-power network protocols, constantly evolving safety and security tasks, and a wide variety of application-dependent, real-time computing loads.

Real-time 3D medical imaging. Medical image processing and analysis are computationally-intensive tasks and require larger memories. The use of programmable chips, like high-powered CPUs and FPGAs, allow real-time, high-speed and accurate processing and analysis of photonic and electronic signals, with high image resolution. It is also comparatively lower priced, flexible, has a longer lifetime and allows continuous update of features and algorithms with the help of software toolsets, such as Altera video and image processing (VIP) suite. This can be used in positron emission tomography (PET), optical coherence tomography (OCT), computerised tomography (CT), X-ray imaging, ultrasound scanning, image guided therapy and so on.

For medical equipment manufacturers. A handheld hardware platform that lets you drag and drop sensor algorithms between the processor and FPGA fabric, and instantly observes resulting trade-offs in performance and power consumption, is being developed by Netherlands based Topic Embedded Products in collaboration with Xilinx. This would serve as a complete clinical reference design platform for medical equipment manufacturers.

In automotive industry. With autonomous driving becoming a reality in coming years, demand for technologically-advanced features, like automated braking, lane tracking, pedestrian detection, traffic sign recognition and parking assistance, have translated into a myriad list of challenges for system designers. With evolving safety, security and reliability standards for a vehicle, FPGAs offer a scalable, highly-reliable and power-friendly platform with reduced form factor and bill of material (BoM). A typical intelligent car has greater than 60 electronic control units (ECUs).

“Designing such a hard, real-time, low-latency gateway unit requires the right combination of hardware and software intellectual properties (IPs), driven by a system software capable of exploiting the best performance from underlying hardware,” says Bhaskar Das of Robert Bosch Engineering and Business Solutions. “The flexibility and scalability offered by FPGAs allow system designers to experiment, benchmark and quickly arrive at an optimal system design that rightly balances hardware and software needs,” he adds.

Which programmable chip is best suited for an application

Here are a few factors based on which the programmable IC for any application could be selected.

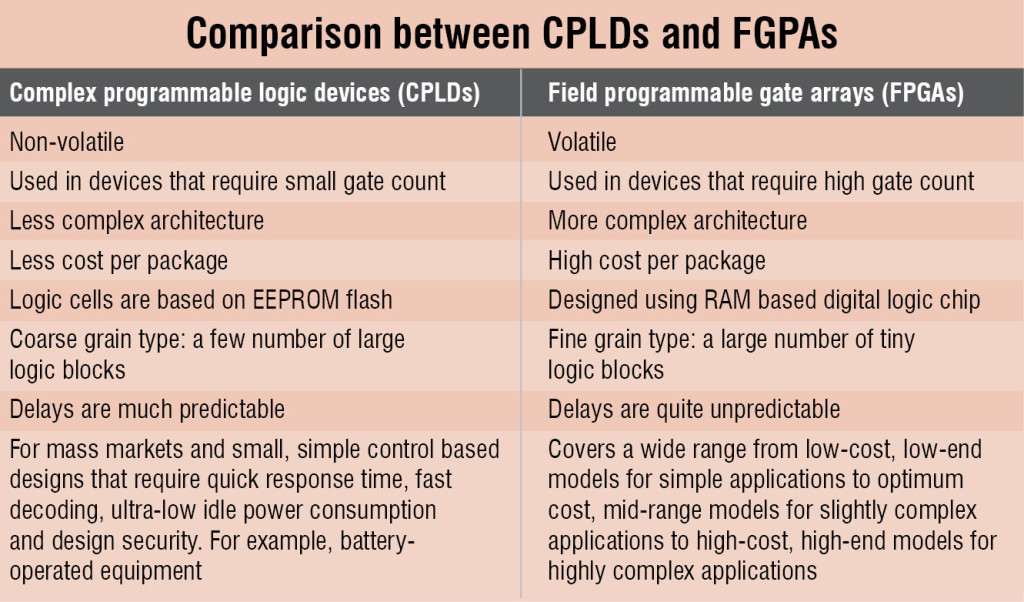

Logic requirement. Logic requirement of an application plays an important role in FPGA selection. If the application is simple and requires only about thousands of logic cells, CPLDs can be used. For low- and medium-complexity projects that require a hundred thousand logic cells or more, low-end and mid-range FPGAs are the options. High-end FPGAs with millions of logic cells are used for very complex applications.

System blocks/design requirement. From simple logic cells, programmable ICs have reached a level of high integration where several features and functions, like DSP blocks, PCIe blocks, processors, mixed signals and memory, are integrated into the chip. Altera’s Arria 10 FPGAs and SoCs have integrated ARM processors, Cypress PSoC integrates configurable analogue and digital peripheral functions, memory and microcontroller on a single chip, and Lattice iCE40 Ultra integrates emerging infra-red remote, barcode, touch, user identification and pedometer functions.

I/O. Input/output requirements, like voltage, SERDES interface standards and others, can be deciding factors while selecting a programmable chip. For example, Altera Arria 10 supports double data rate random access memory (DDR4 RAM) interface with high data rates. Similarly, Xilinx Ultrascale family has a hybrid memory cube (HMC) interface.

Price. The cost of CPLDs is less as compared to FPGAs. Many medium complex designs are more cost- effective at 28nm node of FPGAs. 16nm node is generally for high-end designs and costs more.

What the future holds

Adoption of 14nm FinFET technology has given the programmable industry a much needed boost in terms of high performance, lower cost and lower power, and has bridged the gap between FPGAs and ASICs even closer. Chip manufacturers are now moving towards 10nm technology. Natarajan believes that Intel’s partnership in the programmable space will lead to more breakthrough innovations and allow programmable devices to meet the ever-increasing demand of customers.

Gabriel states that the two emerging trends in the industry—data acceleration and network enrichment—are addressing the need for faster and predictable real-time performance, low-power Wi-Fi and Ethernet connections, and rapidly-evolving device security. “As the industry is struggling to make the IoT work, these two trends play directly into the strengths of, while creating great opportunities for, programmable logic,” adds Gabriel.