SCROOGE TLA grants logic, analogue and mixed-signal design engineers with the capability to quantify power consumption, to track and locate all power peaks. As the logic part of a design is only one face of the coin, analogue designers share the need to address other issues in time domain, beginning with the resilience of switching margins. SCROOGE TLA is an EDA solution that provides the capability to analyse hierarchically the mixed-signal sensitivity to power consumption, which is a key feature for yield optimisation of logic.

Interactive analysis. SCROOGE allows concurrent simulation of mixed-signal transient analysis and power consumption along with display of analogue, leakage and dynamic power consumption as well as intrinsic capacitances for each power supply during transient simulation. It helps in the identification of critical points with current peaks in correlation with intrinsic capacitances.

How it helps in reducing power consumption. The software lets you avoid design oversizing, resulting in improved density and speed. It detects circuit defaults and predicts power consumption much earlier in the flow, thus saving designers’ time by providing them with an easy, efficient and usable solution.

Reducing the peaks of a dynamic mixed-signal power consumption simulation grants the consistent benefit of smoothing-out the disturbances threatening high-resolution analogue parts, including sensitive read-margins of logic parts.

Power analysis is best performed in the time domain, while noise resilience is best analysed over the spectral domain. SCROOGE is an add-on to all the ASIC options supporting logic structural and behavioural languages, empowering the true mixed-signal simulator with capabilities to simulate dynamic power consumption and leakage. Back-annotation of SPEF parasitic capacitances provides the ability to check with high accuracy the model for consumption after layout.

SMASH mixed-signal simulator

As the silicon geometries shrink year by year, device models are becoming more and more complex and the number of elements that must be included in any simulation are invariably on the rise. Today, a simulator must not only accommodate such advances but also provide features and options to allow effective circuit development to be completed.

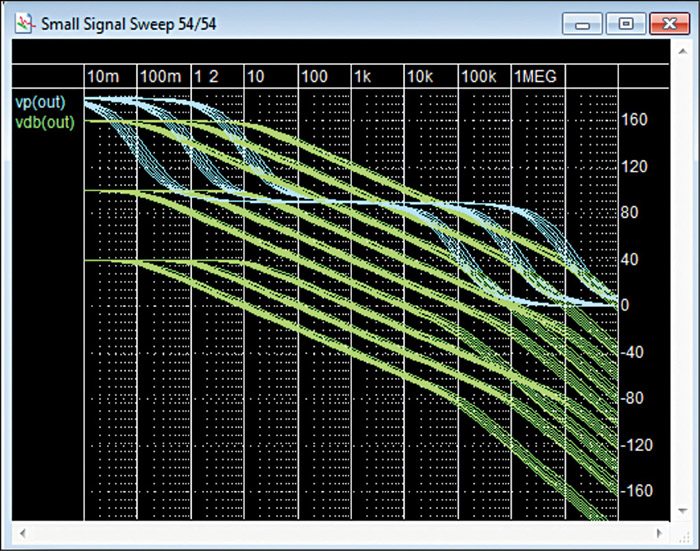

SMASH is a mixed-signal, multi-language, multi-level, single-kernel simulator. Thus it allows device definition in primitive devices or high-level descriptions, handles analogue and discrete-level signals, and recognises a range of net-list languages from SPICE and other high-level description languages. In addition, it allows net-lists to include a variety of the different languages it recognises (electrical, structural, functional and behavioural) while allowing synchronisation of analogue and digital partitions without delay, instability or distortion. The end result is a fast, accurate mixed-signal simulator.

With mixed-signal simulator SMASH, designers benefit from innovative features that enable efficient and fast detection of design defects with a fine control for tuning the speed accuracy trade-offs. These features help designers improve their design productivity for a faster and safer time-to-fab.

Key benefits. SMASH has a state-of-the-art single kernel for easy mixing of multi-language, mixed-signal and multi-domain descriptions. It supports most of the modelling languages like SPICE, Verilog, VHDL, Verilog-A(MS) and VHDL-AMS. It also allows automatic insertion of configurable interface devices as needed between logic and analogue parts.

SMASH has simultaneous display of analogue and logic simulation results in an interactive waveform viewer during the analysis runtime and in post-processing. It has an easy setup of trade-off between speed and accuracy plus added-value features for design bug detection and eradication. The simulator has multi-threading capabilities that help in reducing simulation runtime along with a swift algorithm to accelerate the time-domain electrical simulations of transistor-based circuits.

Intuitive simulation setup. SMASH houses a powerful mixed-signal and multi-language netlisting setup in SLED with dynamic link for cross-probing. It has a user-friendly and intuitive graphic interface for the setup of simulation patterns. The software has features to enable the direct re-use of simulation setup for power consumption analysis with SCROOGE.

How it helps in fast bug detection. The software has in-built dynamic electrical rule checker to automatically detect electrical rule violations for any device, model, net or expression during the simulation. It contains multiple operating point analyses to identify improper operating states that can cause characterisation failures, requiring a design iteration and at worst field failures. SMASH has features enabling import and export of audio files to listen to the output of various applications going from the audio form to physical devices before the prototyping stage. All these features invariably assist in faster bug detection.

The author is a tech correspondent at EFY Bengaluru

Pretty! This wwas an extremely wonderful article. Thanks for providing these details.

This is a topic which is near tto my heart…

Best wishes! Exactly where arre your contact details though?

You can contact us at this link.

I eally love your website.. Very nice colors & theme.

Did you develop this web site yourself? Please reply back as I’m

looking to create my own site and want to find out where you got this frrom orr what the theme is named.

Many thanks!