Targets micro-nano electronic engineering field

FEL targets the engineering field at the micro and nano level with the help of its different tools. On one hand, the collection of Perl modules included provide the engineering support at Verilog or very-high-speed integrated circuit (VHSIC) hardware description language (VHDL) level, while on the other hand, there are tools for embedded design that provide advanced RISC machines (ARM) support as an alternative to Fedora architecture. The extra standard cell libraries included support more than 300MB of cells of size 0.13µm.

Then, there are C based design methodologies, programmable logic array (PLA) tools and simulators for 8051 and 8085 microcontrollers along with the peer-review solution, coupled with Elipse-integrated development environment (IDE) to support the intellectual property (IP) design for digital or embedded hardware, extracted spice decks (sub-circuits with external connectors that appear in an alphabetical order) with simulation facility through gnucap, ngspice or any other spice simulator.

Features that dominate

FEL’s methodologies make it a multi-purpose platform, where at one time it allows design and simulation, while at the other synthesises the design flow.

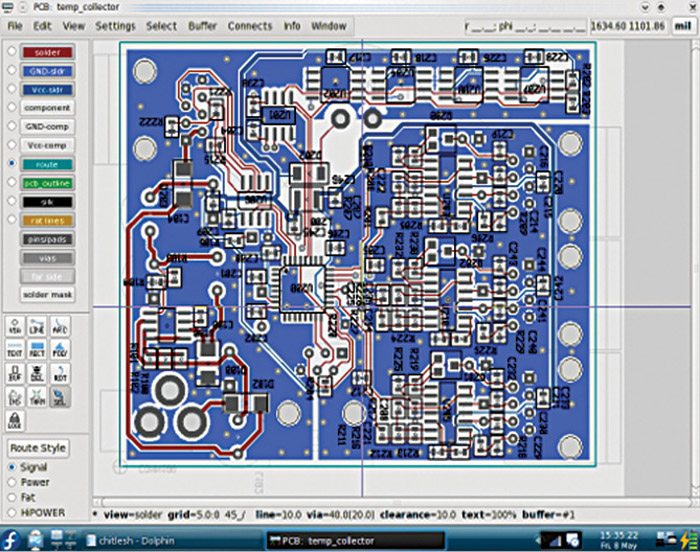

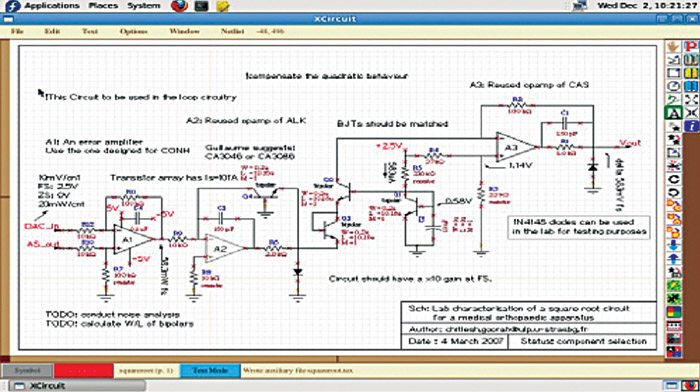

Design and simulation. The application-specific integrated circuit (ASIC) analogue design-and-simulation tool helps designers to edit their schematics and to simulate them. This category includes both general-purpose drawing programs and specific computer aided design (CAD) tools, like XCircuit and various simulators from general-purpose to mixed-level (for example, gnucap, ngspice or gspiceui). When design tools allow one to generate publishable quality of circuit diagrams, simulators perform all types of circuit analysis at a level beyond the capabilities of Spice implementations. These tools are multi-lingual, can mimic different variants of Spice and can also support new languages, such as Verilog-AMS.

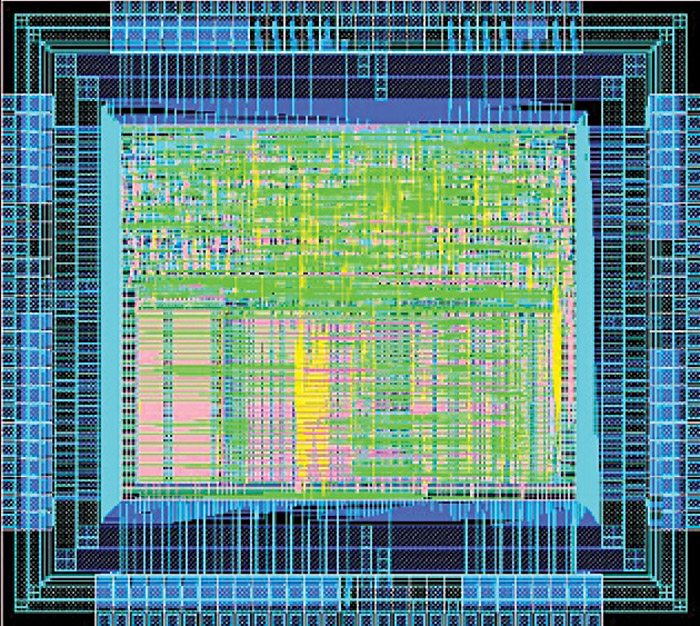

Design rule checks (DRC). FEL platform allows layouts for ASICs using tools like Magic, Electric, Toped and Netgen. These also help in generating database formats, like GDSII stream and crystallographic information file (CIF), from a given layout to enable easy file transfer based on industry standards. During operation, a continuous DRC operates in the background and provides an updated report of the violations in the design, if any. After the design is complete, a hierarchical circuit extractor re-extracts the part of the circuit that has been changed and permits an interactive stretching and compaction, routing the tools to work under and around existing connections.

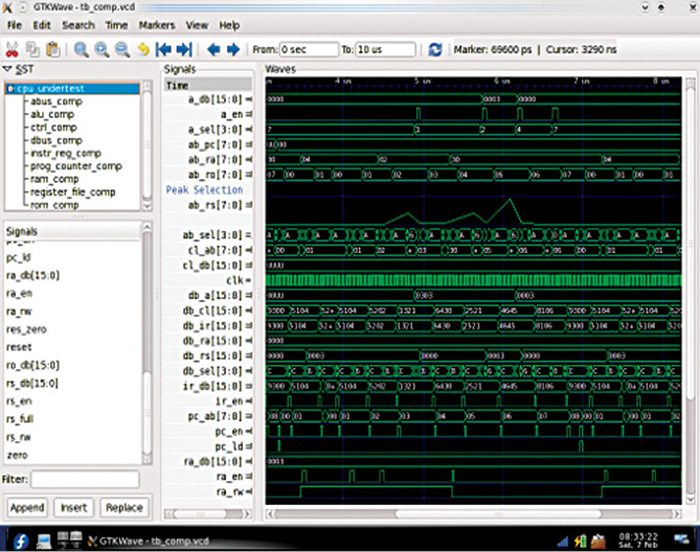

Successful compilation and verification. FEL provides a hardware description language (HDL) simulation environment that allows you to verify functional timing models of the designs. It contains tools like GHDL, quite universal circuit simulator (Qucs), FreeHDL, Icarus Verilog, GTKWave and Drawtiming to scale-up the multiple levels of complexities and abstractions in the design. These support both VHDL and Verilog designs and allow cross-reference generation in HTML. Standard cell libraries help generate automatic layouts from VHDL description, which is then succssfully compiled and run on DLX and LEON1 SPARC processor.