A research-based, open source electronic design automation (EDA) tool written in Java for modern Xilinx FPGAs

Anagha P.

The design and verification of field programmable gate arrays (FPGAs) can be very tiring work due to the time-consuming nature of FPGA compilation processes such as synthesis, mapping, placement and routing. This severely affects the productivity of an FPGA design engineer.

The BYU RapidSmith Project is a set of tools and application programming interfaces (APIs) written in Java language, with the goal of providing users with an easy-to-use platform to work on modern Xilinx FPGAs. Or in simple words, RapidSmith is a do-it-yourself CAD tool for the FPGA models of Xilinx. It offers a compact and fast device database with several APIs to enable different functions for Xilinx devices. RapidSmith project was developed by Brigham Young University, USA. It offers an excellent platform for academia to try out experimental ideas and algorithms for all fields of FPGA CAD research.

RapidSmith is based on Xilinx design language (XDL), which is a fully featured physical design language that provides human-recognisable format of Xilinx’s proprietary native circuit description (NCD).

RapidSmith eases the difficulties of using XDL. It is mainly aimed at the use by academia in all fields of FPGA CAD research, and lets the researchers import XDL/NCD files, manipulate, place, route and export designs and perform a variety of design transformations. It also contains packages which can parse or export bitstreams at the packet level, and represent the frames and configuration blocks in the provided data structures. It can resolve, manipulate and export bitstreams according to documented methods of Xilinx.

RapidSmith is not a replacement for Xilinx ISE design suite. It can be used only with a current valid licence to Xilinx tools installation. Any person with a basic knowledge in programming and Java and a good understanding of Xilinx FPGAs and XDL can easily operate this tool.

Licence

BYU RapidSmith Tools is a free software which comes under general public licence (GNU). One can redistribute and/or modify it under the terms of GNU GPL. The main purpose of this package is that it can be used as a research tool, and should not be used for designs bound for commercial purpose.

Supported devices

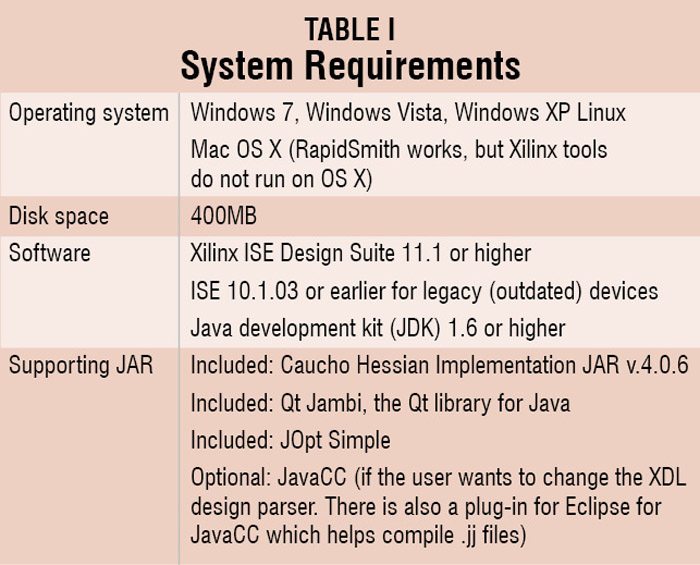

RapidSmith is supported in Virtex 4 and 5 families in all forms and applications. It can create device files for all modern Xilinx FPGA families and hence can support, though to a lesser extent than Virtex 4 and 5, for other Xilinx FPGA families too. In the case of legacy device families, the design suite version ISE 10.1.03 or earlier may be required. The compatible features of various families are shown in Table II.

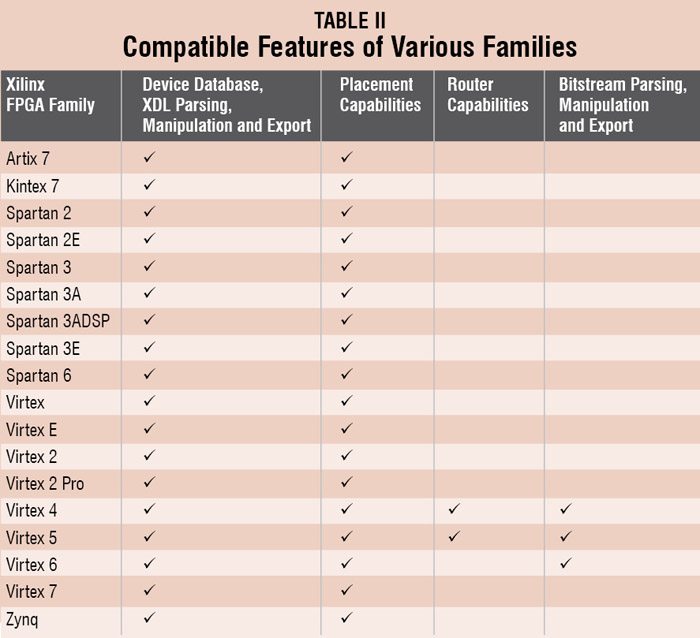

Installation

First you need to ensure that the Xilinx tools and Java development kit are on your PATH. Add all the supporting JAR files in the JAR folder (hessian-4.0.6.jar, jopt-simple-3.2.jar, qtjambi-4.6.3.jar and qtjambi–4.6.3.jar) to your CLASSPATH environment variable. Also add the RapidSmith Java project to CLASSPATH environment variable. Now you need to create an environment variable RAPIDSMITH_PATH and set the value to the path of Java project located on your computer.

In case you are using the RapidSmith for a legacy Xilinx device such as Spartan 2/2E, Virtex or Virtex E/2/2Pro, ISE Design Suite 10.1 or earlier will be required. The program should be pointed to the appropriate installation of tools. For this, we use an environment variable XILINX_LEGACY_PATH and set its value to bin path of the design suite tools. For example, XILINX_LEGACY_PATH=/opt/xilinx/10.1/ISE/bin/win32 will use the 32-bit tools of ISE 10.1 of a Windows installation. Skip this step if you are not using an outdated device.

Next we have to compile all the Java classes. This is done automatically if the project is imported to an IDE—like Eclipse. Now test the installation by running any of the programs.

Overview

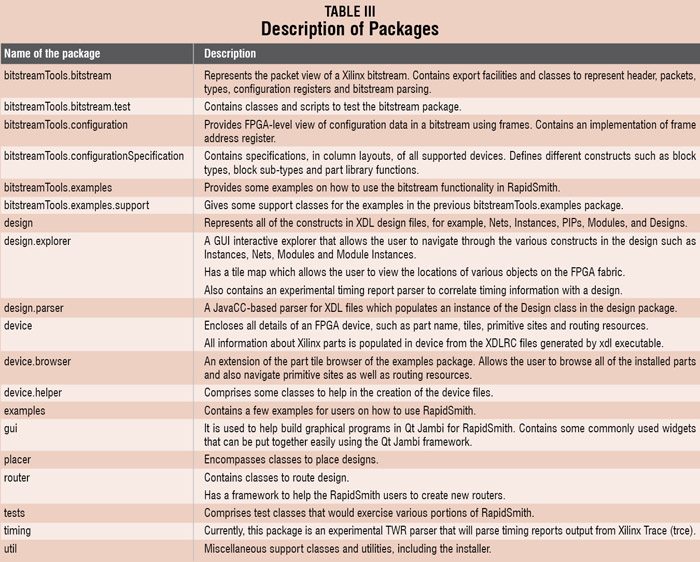

RapidSmith is organised into several packages. These packages and their description are listed in Table III. All these packages are prefixed with edu.byu.ece.rapidSmith.

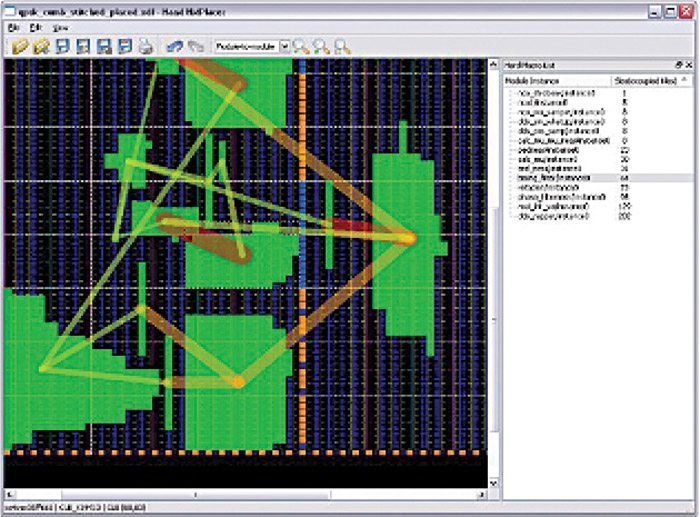

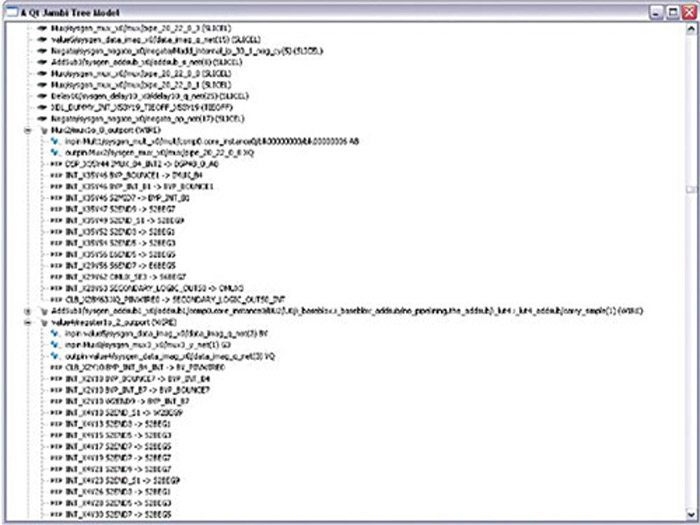

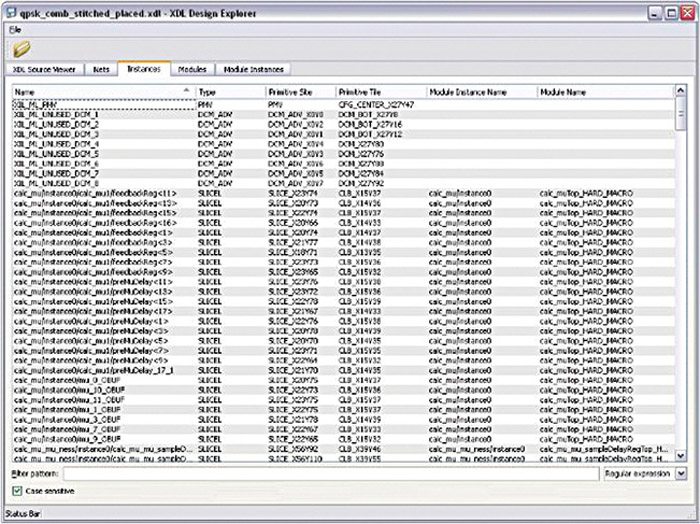

Design analysis tools

RapidSmith provides a simple platform to create design analysis tools for a given design in XDL format. Consider the simple design browser tool given in Fig. 1. It is a screenshot of a tree-based graphical list traversal of an XDL design file. Here you can see primitive instances, pins and routing protective Internet protocols (PIPs). The screenshot of a similar tool is provided in Fig. 2, which shows a program using RapidSmith, with the ability to interactively search for primitive instances in a loaded design. Yet another example is the design analyser which tabulates detailed resource utilisation statistics and design properties.