So, you are working on your circuit design and your Verilog code is ready! You have tried your hand at simulation and the code is functioning correctly. What next? Synthesis is the answer. Yosys is a framework for Verilog RTL synthesis. It is an open source tool for performing logical synthesis. Falling under Internet Software Consortium (ISC) licence category, it is a free software that takes in your Verilog/Very high speed integrated circuit Hardware Description Language (VHDL) code and gives out a gate-level netlist that your printed circuit board (PCB) designing software understands.

How it helps

With presence on Reddit, Stack Overflow and GitHub (github.com/cliffordwolf/yosys), the tool can run on Ubuntu, Fedora and Windows operating systems (OSes). Here are a few features that would keep you thinking about the experience, long after you have finished working on your design.

With most synthesis tools being proprietary, Yosys is one tool you can easily download and start working with your code anytime you want. To work with Yosys, you will just need a C++ compiler with C++11 support and a few tools like GNU Flex, GNU Bison and GNU Make.

Yosys reads your Verilog code, supporting Verilog 2005 version, converts it into its internal format, elaborates the design to establish design hierarchy, performs optimisations and converts the code into a netlist.

Standard algorithms. There are a variety of algorithms, called passes, to perform register transfer level (RTL) behavioural and logic synthesis of your code. These are modelled to suit different applications, and you can modify these to suit your requirements using synthesis scripts.

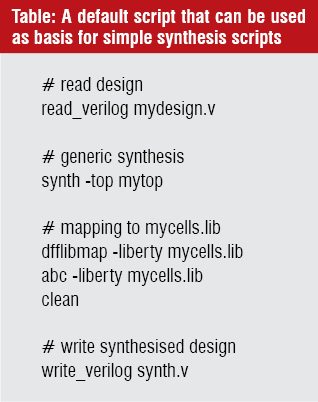

A synthesis script is simply a file with commands that will be executed in sequence on the file being read by the tool. The table (next page) shows a basic synthesis script that can be used to synthesise most designs. You can even add additional passes to existing ones by extending Yosys C++ code base. This is further made easy by making sure all passes use the same interface, so as to ease the effort from the user to understand or modify the source code. Yosys even supports multi-bit values and multi-port memories.

Flexibility. You can choose to generate three kinds of netlists, namely, a simple RTL netlist that describes the circuit in terms of registers and data transfer, a complementary metal oxide semiconductor (CMOS) gate-level netlist that converts a circuit to its basic form characterised by CMOS gates and a coarse-grain netlist that reduces the design to an implementation of coarse-grain cells. The netlist you obtain is simply decided by which technology library you map the design to.

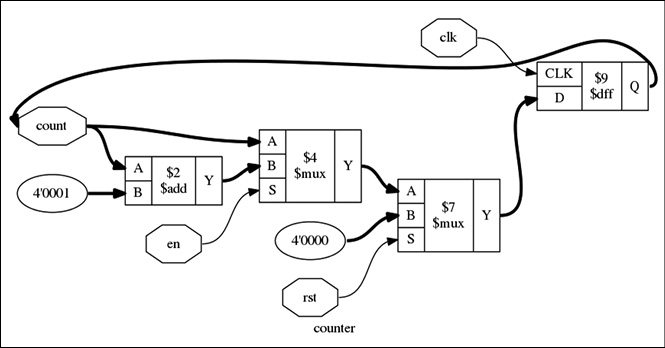

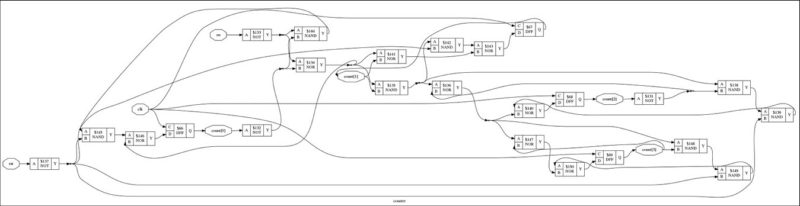

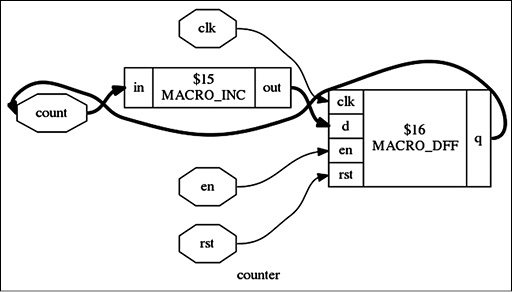

Visualise how your design looks. With the tool, you can view this netlist in a gate-level representation, that is, a diagram consisting of the circuit design in terms of basic logic gates. In effect, cells that represent the corresponding function replace all operators and logic. When command show is used for a netlist, it invokes an open source software for graph visualisation called as Graphviz. This then converts the netlist into a pictorial representation for the user to observe the design.

Interactive navigation. To analyse and investigate designs, it is often required to not just view circuit diagrams but also narrow down and scrutinise their interesting parts. Yosys allows you to change the appearance of the circuit diagram and save it in the name and format you wish. Instead of waiting for the synthesis process to complete, you can simply add command Shell at the point you want to check in the design. Synthesis is stopped at that point for you to interact with the design. Yosys also allows you to perform different types of synthesis on different sections of the code at one go.

Interactive navigation. To analyse and investigate designs, it is often required to not just view circuit diagrams but also narrow down and scrutinise their interesting parts. Yosys allows you to change the appearance of the circuit diagram and save it in the name and format you wish. Instead of waiting for the synthesis process to complete, you can simply add command Shell at the point you want to check in the design. Synthesis is stopped at that point for you to interact with the design. Yosys also allows you to perform different types of synthesis on different sections of the code at one go.

Exchange between formats. When you talk about parsing designs and exchanging sequential logic between programs, formats like Berkeley Logic Interchange Format (BLIF) and bit-precise word-level format or BTOR come to the fore. All you need are simple commands that convert your Verilog design into these formats, and vice-versa.

More than just synthesise. Not just synthesis, Yosys lets you perform advanced analysis and circuit transformations. You can extract finite state machines and perform operations on these. It also offers minimum support to frequent sub-circuit mining and technology mapping by finding sub-circuit isomorphism.

Latest additions. Yosys 0.5 sports a log file even for warnings obtained while synthesising your code so as to make sure your design can be re-worked to perfection. Flip-flops with an enable signal promise to be a boon for digital circuit design. Commands for equivalence checking, block random access memory (BRAM) support, enhanced commands, drivers and performance improvements add a spark to Yosys.

Mapping to the technology library

One of the main aim of synthesis is to map your design to a particular technology library. To understand why this step is necessary, imagine you are drawing a circuit layout. The first thing you would need is the size or the fit-to-scale factor. In other words, the technology library provides the basic unit in the design of the layout. Yosys has an inbuilt technology library consisting of basic CMOS cells.

To map to the library, use command abc [options] [selection]. This invokes ABC, a software system that synthesises and verifies your logic design using scalable optimisation techniques. ABC then maps the internal gate library of Yosys to the target architecture. To validate the logic formula in the design, Yosys takes help from MiniSat, the SAT-solver library.

To map to the library, use command abc [options] [selection]. This invokes ABC, a software system that synthesises and verifies your logic design using scalable optimisation techniques. ABC then maps the internal gate library of Yosys to the target architecture. To validate the logic formula in the design, Yosys takes help from MiniSat, the SAT-solver library.

The Yosys flows

You are free to choose the best format for your design and allow data to flow from input to output in a sequence. The main difference between these flows would be the mapping to library cells. A straight-forward application-specific integrated circuit (ASIC) design is mapped to simple CMOS cells. When synthesising for field programmable gate array (FGPA) based designs, the design has to be mapped to look-up tables (LUTs) that are stored in the library.

Yosys interconnects to Xilinx library to allow for your FPGA to be designed. For logic mapping to digital signal processing (DSP) cells in FPGAs, or synthesis for custom coarse-grain reconfigurable hardware, you can choose to go with the coarse-grain architecture. These cells operate on bit-vectors, instead of single-bit signals, and accelerate the process.

Check for correctness

As soon as you install your tool, check if it is functioning right. Yosys-bigsim on GitHub provides a variety of real-world Verilog designs and test benches.

VlogHammer is used to check the correctness of the Verilog front-end of Yosys. This currently tests combinatorial circuits described by Verilog expressions by comparing the results from Yosys with other synthesis-tool results, while at the same time also cross-verifying using various simulation engines.

Coming to the verification of your design, a symbolic model check (SMC) formally checks the properties of your circuit. To check if two circuits function identically, you may reproduce a circuit. You may also check the design at two different stages of tool processing, to perform a formal equivalence check. You can also check if a module conforms to interface standards.

What more would you like

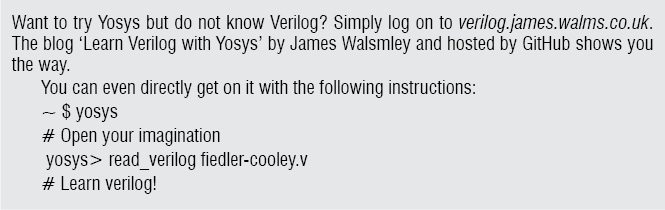

Using Emscripten, an exclusive JavaScript port is being developed for Yosys. Called YosysJS, it is meant for building Web applications for educational purposes. When you contrast Yosys with proprietary tools, the main drawback is advanced-level synthesis for timing, power and such factors. May be future releases could see a tweak in Yosys that would cater to these features and much more. Stay tuned to its website www.clifford.at/yosys for regular updates.

For more information: click here