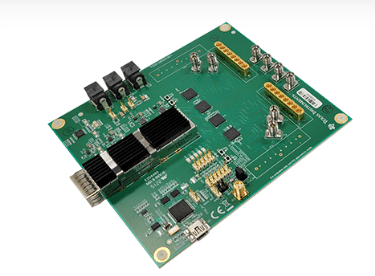

This reference design effectively uses the DS560DF410 retimer in a versatile, high-performance MCB suitable for various high-speed data communication applications.

The 56G PAM-4 retimer DS560DF410 is crucial for boosting high-speed data communication systems’ performance and reliability. It equalizes and extends high-speed signals in environments with compromised signal integrity due to long distances, loss, and crosstalk. Independently locking to symbol rates (PAM4 and NRZ) from 19.6 to 28.9GBd or any supported sub-rate, the DS560DF410 ensures robust signal transmission, making it essential for data center switches, campus and branch switches, edge routers, and core routers.

This reference design TIDA-060043 by Texas instruments illustrates the implementation of the 56G PAM-4 retimer DS560DF410 for equalizing high-speed signals in active electrical cable applications. The design is a Module Compliance Board (MCB), which routes signals from a QSFP-DD connector through a retimer to SMA and MXP connectors in both ingress and egress directions.

The design features eight independent channels for each direction, ensuring comprehensive signal management. It is compatible with QSFP-DD cables for both ingress and egress, and also supports host-side Huber-Suhner and SMA compatibility in both directions. Configurability is achieved through electrically erasable programmable read-only memory (EEPROM) or USB-to-I2C communication, providing flexible control options. Headers for all relevant debug and configuration pin controls and interrupts are included, enhancing troubleshooting and customization capabilities. Additionally, the design includes onboard power regulation for converting 3.3V to 1.8V and 1.2V domains, ensuring stable power supply for the retimers.

The primary applications of this design include data center switches, campus and branch switches, edge routers, and core routers. MXP connectors, commonly used in high-speed test and evaluation equipment, were selected for interfacing with this MCB due to their prevalence in TI’s 25G/28G and 56G Ethernet signal conditioning device EVMs.

High-speed trace layout is critical in high-speed design. In this MCB design, layout recommendations from the DS560DF410 56Gbps Multi-Rate 4-Channel Retimer with Crosspoint data sheet were meticulously followed to ensure optimal performance. The board is powered with 3.3V, while the DS560DF410 retimers operate on the 1.8V and 1.2V domains. The 3.3V to 1.8V conversion is handled by the TPS7A52, and the 3.3V to 1.2V conversion is managed by the TPS62867, consistent with the DS560DF410EVM design.

The DS560DF410 is a four-channel multi-rate retimer with integrated signal conditioning. This device enhances the reach and robustness of long, lossy, and crosstalk-impaired high-speed serial links. Each channel in the DS560DF410 independently locks to symbol rates (PAM4 and NRZ) in a continuous range from 19.6 to 28.9GBd or to any supported sub-rate.

The TPS62865 and TPS62867 are high-frequency synchronous step-down converters, providing an efficient, flexible, and high power-density design. The TPS7A52 is a low-noise (4.4 µVRMS), ultra-low dropout linear regulator (LDO) capable of sourcing 2A with a maximum dropout of only 65mV. The device’s output voltage is adjustable from 0.8V to 5.2V using an external resistor divider, offering precise voltage control.

TI has tested this reference design. It comes with a bill of materials (BOM), schematics, etc. The additional data about the reference design on the company’s website. To read more about this reference design, click here.