Enhancing electric vehicles and energy systems with cutting-edge technology to optimize performance and extend lifespan.

Battery Management Systems (BMS) play a pivotal role in high-end battery-powered applications like electric vehicles and energy storage systems. Their primary role is to safeguard the health of all cells within a battery pack, ensuring optimal power delivery for the required application. Furthermore, they act as a protective shield, preventing cell damage and ensuring every cell operates within the suggested conditions set by the manufacturer. This not only ensures efficient performance but also prolongs the battery pack’s lifespan.

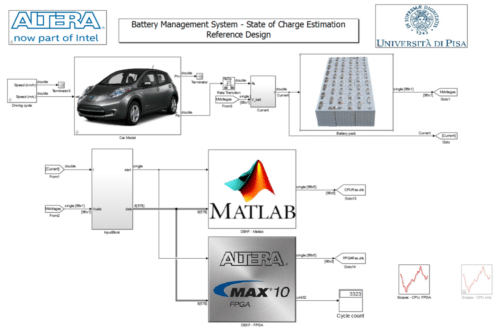

The Altera BMS Reference Design from Intel showcases how to estimate battery state of charge (SOC) on an FPGA-based real-time control system. This platform can be further enhanced to incorporate additional BMS features like monitoring the battery’s state-of-health and ensuring charge equalization, also known as cell balancing. This design leverages a dual extended Kalman filter (DEKF) algorithm to determine SOC for up to 96 cells, with the help of a MAX 10 development kit. FPGAs serve as versatile and potent platforms for BMS solutions. Their extensive I/O capabilities make them suitable for parallel connections to multiple battery modules. Moreover, they can expedite complex calculations, such as state-of-charge estimation, with efficiency.

The BMS Reference Design boasts several notable features. The design offers various hardware strategies for SOC calculations. One method employs the Nios II processor with floating-point acceleration. Another method merges the Nios II with floating-point acceleration and a floating-point matrix processor. A third method blends the Nios II processor with the DEKF algorithm within a dedicated floating-point IP. Impressively, the system-in-the-loop simulation operates a MATLAB Simulink model which communicates directly with FPGA hardware through the Altera system console API. This setup facilitates real-time comparison of results from the FPGA with those derived from Simulink calculations. Additionally, the Nios II processor manages scheduling and liaises with MATLAB via the System Console. Lastly, the operational backdrop for the Nios II software is the μC/OS-II real-time operating system.

This reference design comes with the Altera MAX 10 FPGA development kit (rev C). The BMS reference design necessitates specific software components for optimal functionality. This includes the Altera Complete Design Suite version 15.0, encompassing the Quartus II software v15.0, DSP Builder v15.0, and the Altera Nios II Embedded Design Suite (EDS) v15.0. Additionally, MATLAB R2015a is also required for the design’s operation. To read more about this reference design, click here.