Design architects are now more comfortable selecting a field-programmable gate array (FPGA) as the central piece on the board. Given the quantum of vendor and community resources available at their disposal, FPGAs makes it easier for them to complete their design within stipulated timelines and budget.

FPGAs are now capable of serving as suitable alternatives to application-specific integrated circuit (ASIC) or application specific standard product (ASSP) implementations in many systems—so much so that some vendors are marketing their FPGAs as ASIC-likes.

Neeraj Varma, director of sales at Xilinx explained in an interview, “The whole belief is that the FPGAs in UltraScale generation have a lot many more features that are ASIC-like. The key here is the ASIC-like class architecture. There are several changes we made in the architectures that are like ASICs. ASICs are always good in power and performance.

“FPGAs, traditionally, have an overhead, but we are trying to bridge this gap, and we did quite well in 28nm. But in 20nm, we are going to do even better.”

Earlier, FPGAs had few global clocks. As the density grew, skew problem also increased. Vendors, such as Xilinx, added more clocking regions, resulting in more clocking resources placed at different areas of the chip. This is how exactly it is done in ASICs to solve skew problem, and this is the reason why it is called an ASIC-class clocking.

Here, the software used is also an ASIC-strength design suite. The design suite has many built-in features where you are not allowed to make any mistakes, similar to how it is done for ASIC design tools. The tool itself takes care of so many things, saving your valuable time in repeating the design process.

Denser FPGAs

One of the points I came across in a white paper from Altera was that, because of shrinking of design cycles and design teams, cost-conscious designers were trying to move away from multi-chip solutions that were too costly and lacked flexibility. They were also moving away from single-chip solutions that could not meet power or performance objectives, or ASIC systems on chips (SoCs) which are too slow to get to market.

ARM-based SoCs combine a hard ARM processor, memory controllers and peripherals with customisable FPGA fabric in a single SoC. Initially, FPGAs were not dense enough and did not have hard cores on them.

from Xilinx

Now, even for a single family of product, the user has quite a few options to select from, such as ARM-based SoCs that are user-customisable. This helps reduce system power and board size while increasing system performance by integrating discrete FPGAs, digital signal processing (DSP) and microprocessor devices into a single, user-customisable SoC.

The built-in hardcore IP cores, which were not present earlier, are available now, providing more predictable performance figures. Every year we see shrinking of the process node in line with the industry growth and Moore’s Law. Now 45nm, 28nm, 20nm and 16nm FPGAs are available. Also, now we are moving towards 14nm and 10nm nodes. This favours better density and reduction of power.

Adaptive look-up tables

Over the years, the basic building block of the FPGA logic fabric—the look-up table (LUT) based function generator—has remained almost the same. Experimentations were done with the number of inputs for LUT such as three, four, six and eight. Now they have adaptive LUTs which allow two outputs per LUT with two function generators to be implemented, sharing some of the inputs. The FPGAs mainly evolved by providing the same set of resources with different number of resources per family.

In addition, today it is all about providing ecosystems to the designer—evaluation boards, reference designs, design communities and partner IPs, ensuring FPGAs are able to meet the stringent time-to-market goals of the customer.

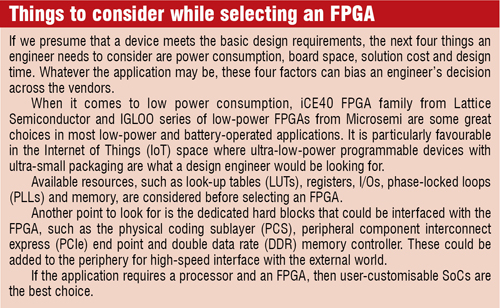

Selecting FPGAs

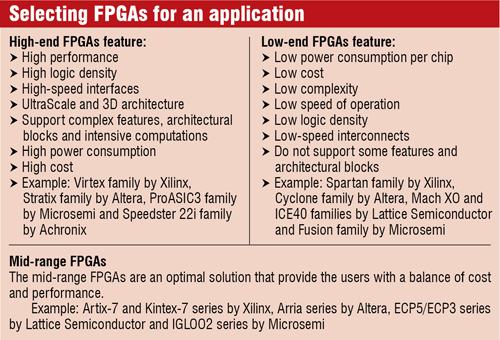

Over the past few years, a distinct segmentation of FPGA vendors has occurred depending on the device capabilities: distinct high-end and low-end product lines. If the application requires intensive computation, the FPGAs preferred are those with complex DSP blocks, high-speed inputs/outputs (I/Os) and configurable memories. They are seen serving consumers looking at ultra-high-definition televisions, 3D televisions and medical applications, such as 265-channel ultrasound. Examples of FPGAs delivering these requirements are Virtex, Stratix, ProASIC3 and Speedster 22i.

For low-cost applications, where a trade-off has to be made for performance, FPGA families, such as Spartan, Cyclone ECP5 and Fusion, are used. Typical applications include emerging communication products, such as heterogeneous networks (HetNet), gigabit passive optical network optical line terminals (GPON OLTs) and small form-factor pluggable (SFP) modules.