Intellectual property (IP) cores are standalone modules that can be used in any field programmable gate array (FPGA). These are developed using HDL languages like VHDL, Verilog and System Verilog, or HLS like C.

IP cores are part of the growing electronic design automation (EDA) industry. In this article, these will be discussed with respect to SRAM based FPGAs.

Let us take an example of universal asynchronous receiver-transmitter (UART) IP block, which is intended to be used in different applicatons. The developed UART IP core module should:

• Meet basic UART functionalities

• Be portable, so that it can be used in any vendor technologies; for example, Xilinx/Altera as plug and play

• Have user-configurable parameters (like baud rate)

• Have processor interface/generic parameter file to modify configurations as required

• Provide IP data sheet

Types of IP cores

IP cores can be categorised as hard IP core, firm IP (semi-hard IP) core and soft IP core.

Hard IP cores.

These are part of the FPGA-independent modules; for example, PCIe or Ethernet IP modules available in Xilinx FPGA. You have to configure the location and provide interface connectivity with other modules, clocks and resets. Since these blocks are already part of the FPGA device, these will not be taken into account while calculating the utilisation of the slice logic report. In the utilisation summary, these will be counted as the number of PCIe/Ethernet blocks used. Because of a fixed location in the FPGA, these cores cannot be ported to other FPGAs. Neither can these be reused like HDL components, if already used in the FPGA.

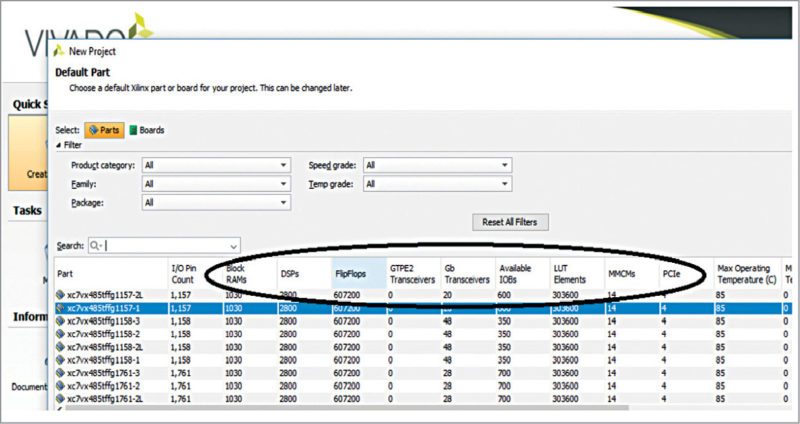

Fig. 1 shows Xilinx Vivado tool – FPGA selection window for Virtex-7 FPGA with internal hard IP details for creating the project. The number of hard IPs may vary between different FPGA families.

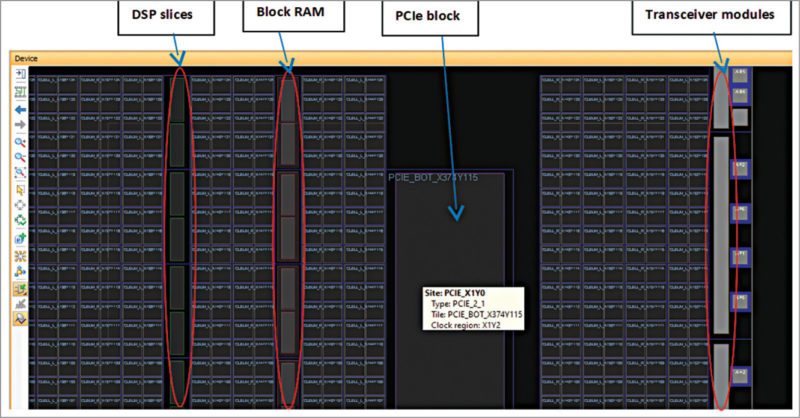

Fig 2. shows the dedicated location of the hard IP in Virtex-7 FPGA.

Unmarked (not labelled) areas (between DSP slice and block RAM, or block RAM and PCIe, or PCIe and transceivers) in the FPGA (Fig. 2) contain large distribution of flip-flops, latches, multiplexers, LUTs, etc. Soft IP cores or custom logic are implemented in these areas.

Advantages include:

• Timing violations minimised

• No extra cost, that is, cost of the hard block is included in the FPGA; hence, can be considered as low-cost compared to other two types of IP cores

• No individual licence, except for compiler tool licence

• RTL code maintenance reduced

• No extra documentation required; for each IP level, documentation provided by vendor

• For slice/LUT summary, hard IP cores not considered

• Low dynamic and static power can be achieved if hard IP blocks are used in the designs

• Functionality and performance guaranteed

• Fully-tested and with known errors/limitations, if any, as per documents provided by vendor

Disadvantages include:

• Not portable; these are highly optimised and targeted at specific FPGAs

• Fixed implementation with pre-defined constraints

• Limited availability of number of hard IPs with respect to particular FPGAs

Firm IP cores.

Firm IP cores are also known as semi-hard IP cores. These are a form of gate-level netlist, where you have the flexibility to place the module in the FPGA as per usage and with minimal user-programmable configurations.

For example, if a third-party IP is targeted at Xilinx FPGA, then the IP provided will be .ngc file. You can integrate this file with your project and instantiate it as a component in the top level to interconnect with other modules, and then proceed with synthesis.

To use a firm IP core, you should have proper FPGA resource planning and requirement specifications before procuring the IP for the project.

Xilinx Coregen-generated IP cores (like FIFO, shift registers and memory interface cores) can be grouped into the firm IP core category. You have to include .ngc/.xco in the project directory (for Xilinx), and specify the instantiation in the top file. Instantiated components can be moved around within the FPGA to meet performance and timing.

Advantages are:

• Modifications allowed to some extent

• Functionality and performance are measurable

• Resource utilisation considers firm IP logic area

• Completely tested

• Documentation may be available up to some level

Disadvantages are:

• Limited portability

• Modifications to source not possible

• May be licensed based on cost

• Source utilisation matters while considering the FPGA

• Timing/performance may have impact

Soft IP cores.

These are completely flexible and do not depend on vendor technology. These can be ported across various FPGA platforms. The IPs are developed using HDL languages and you are provided with source codes, so the IPs can be modified according to your application and easily integrated with your modules. These are reusable and can be targeted at many variants of FPGAs.

In Xilinx FPGAs, ARM, Zynq and PowerPC processors fall under hard IP category, whereas Microblaze falls in the soft IP group.

Similarly, in Altera, ARM, Intel ATOM processors come under hard IP core, and Nios-II processor under soft IP core.

Examples for other soft IP cores are 8051 microcontrollers IP, I2C controllers, SPI controllers, standard bus interfaces or any open core whose source can be modified.These modules should be used as primitive instantiation in the custom RTL so that these get connected to user logic. In some cases, DDR2/3 cores are also specific to some banks of FPGAs.

Advantages are:

• Portable across FPGAs, independent of target technology/vendor

• Available as open source IP

• Easy to modify and implement as per custom applications

• Complete data sheet/documentation available for originally-targeted device/technology

Disadvantages are:

• IP cost may be high when compared to firm IP core since source code provided by third party

• Individual IP core licence may be required

• Performance/timing may vary with originally-targeted device/technology

• Documentation might be generic or specific to originally-targeted device/technology

• Support may not be available (or limited support available) for custom modifications

• Extra effort required while targeting custom technology/device

• In-depth understanding of design required before modifications can be made

Several factors must be considered while selecting the suitable IP such as cost of IP, effort required for customisation (for soft IP core), time to market, FPGA family, availability of simulation environment (unit and integrated levels) of IP, documentation, board-level evaluation of IP and support during development, among others. Nowadays, since most basic IP cores come with FPGA implementation tools for free, it makes time-to-market faster and results in lower costs.

In this article, we have taken Xilinx and Altera as examples. But you can find other vendors as per your FPGA designs. So depending on complexity, timeline and overall project cost, you can choose proper IP core type.