Power versus performance is an ongoing battle, with the best involving a compromise between the two. High-performance system(s)-on-chip (SoC) designers often struggle to achieve the best possible power-performance balance. Customers’ user experience is an important aspect to consider as it determines performance improvements. However, this calls for increasing the battery size as most devices are battery-powered. Memory tracker technology from Performance-IP, for example, enables low power processors to operate at higher efficiency.

Power reduction techniques for processors

A typical SoC design consists of processors, memory clients, interconnects and memory systems. Processors are one of the major power consumers in a device, so switching off the CPU when idle helps. This includes turning off the processor when all processes are blocked, when processes appear to be busy waiting and extending real-time process sleep periods. Studies have shown these to increase battery lifetime by approximately 20 per cent in Apple systems.

These tricks are often used by processor designers as well. Dynamic power consumption in a processor arises from circuit activity. As performance, that is, speed and frequency, of the IC increases, the amount of dynamic power also increases. Dynamic power is data-dependent and closely tied to the number of transistors that change states. A hidden component of dynamic power is loss due to dynamic hazards. This must be taken care of while designing power-conscious processors.

Architectural changes to reduce power

Crusoe from Transmeta is a very long instruction word (VLIW) processor designed for low-power applications including mobile PCs and Internet devices. It allows microprocessors to emulate Intel X86 instruction set. Instead of the instruction set being implemented on the hardware, Crusoe runs a software abstraction layer known as code morphing software.

This has brought about a reduction in required power. Intel processors at 400MHz used to consume about 7.4 watts, or AMD clocked at 700MHz at the time consumed 34 watts. The 700MHz Crusoe uses one watt, which was a revelation when introduced.

LongRun in Crusoe, monitors the precise performance level needed by an application and dynamically adjusts the processor’s operating speed and voltage to match it. This increases the battery life by a significant amount.

Following this, there is SpeedStep from Intel that allows clock speed of the processor to be dynamically changed by the software. It allows the processor to meet the instantaneous performance needs of the operation being performed, thus minimising power consumption and loss through heat.

LongHaul is a speed-throttling technology developed by VIA Technologies that helps reduce power consumption. It uses specialised instructions utilised by the software to exercise control on bus-to-core frequency ratio and CPU core voltage. When the system boots up, ratio and voltage are set to hardware defaults. Depending on the load on the CPU, a CPU driver controls the throttling during operation.

Following a similar course, AMD’s dynamic frequency scaling and power saving known as PowerNow (mobile chips) and Cool‘n’Quiet (desktop and server chips) allowed adjusting clock speed under varying loads and idle conditions to save battery power. These power-saving techniques allowed power saving but, caused problems with the operating systems. Microsoft also reported problems previewing video files with SpeedStep enabled under Windows 2000 or XP. This called for making further changes, resulting in newer protocols that are being implemented today.

Power saving for the present

Building up on PowerNow, AMD launched Turbo Core beginning with Bulldozer architecture. The architecture focused on reducing power consumption over the earlier K10 architecture for higher performance per watt.

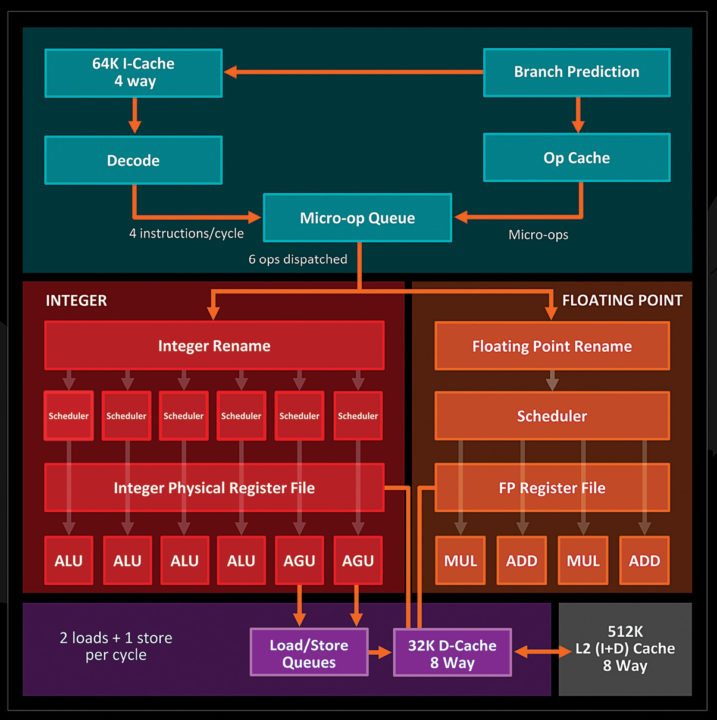

Bulldozer processors are based on GlobalFoundries’ 32nm silicon on insulator, which reuses DEC approach for multitasking computer performance. By eliminating redundant elements that creep into multi-core designs, it aims to take advantage of its hardware capabilities while using less power.

This is followed by Zen architecture that looks to define balance between power and performance. As per multi-threaded Cinebench R15, performance per watt is more than double than it was for Piledriver architecture.

Zen architecture includes a complex stack engine that can eliminate certain stack manipulation instructions. This coupled with the core design, which is optimised to use less power, is something to look out for. It has an integrated power management controller that monitors and adjusts the voltage used by each core according to the temperature and loading.

Unlike previous versions, power management roles are baked directly into silicon and are out of the control of the software and operating system. The hardware on the chip can respond in a matter of milliseconds, allowing much tighter control over voltages and clock speeds.

Balancing power and performance.

Intel Turbo Boost draws a parallel with Turbo Core from AMD. However, Enhanced Intel SpeedStep Technology is more power conscious and allows the system to dynamically adjust processor voltage and core frequency, decreasing average power consumption and heat production.Design strategies in SpeedStep involve separation between voltage and frequency changes. Varying voltages in small increments separately from frequency changes allow the processor to reduce periods of system unavailability occurring during frequency changes.

The system can transition between voltage and frequency states more often, hence providing improved power-performance balance.

Clock partitioning and recovery is another method for reducing power consumption. The bus clock runs during state transition between the core clocks, and phase-locked loops are stopped while the logic remains active. The core clock can also restart more quickly under SpeedStep than under previous architectures.

Ultra low power processors for wearable devices

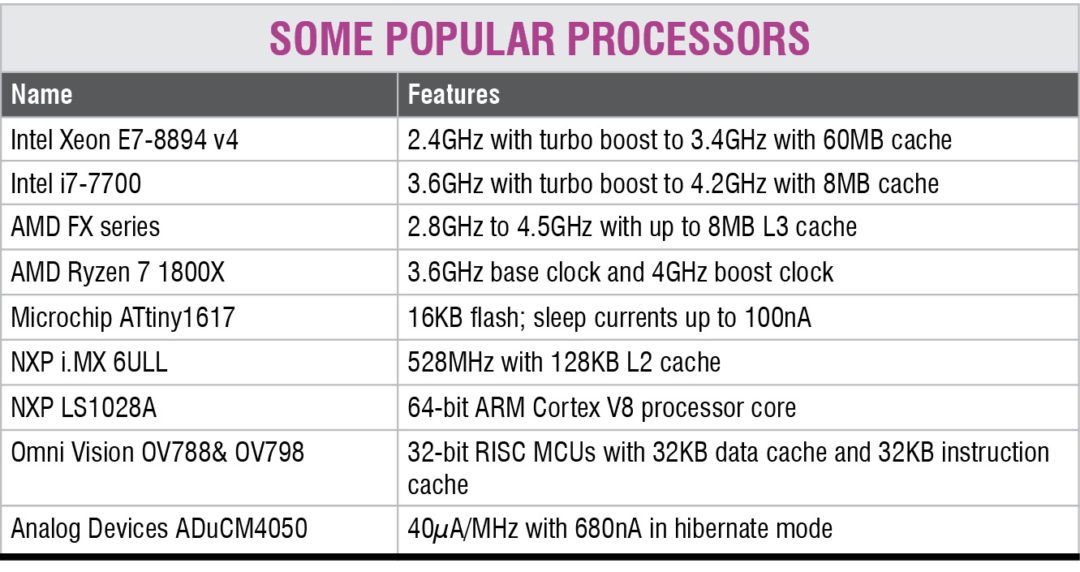

A lot of power is also being saved by reducing consumption in MCUs. The requirement is to have processors that can increase battery life. This has led to a lot of processors with power consumption in µA/MHz, and it is further reducing. STMicroelectronics’ STM32L496 and STM32L4A6, for example, work at 37µA/MHz. Kinetis L series MCU from NXP work at about 75µA/MHz.

Among the wide range of ultra-low-power MCUs, however, ARM Cortex-M processor seems to be the common link. Certain modifications are added to the underlying Cortex core to further improve consumption. For instance, a bit manipulation engine improves time and code size in the architecture.

Kinetis from NXP employs it to the highest effect. Low-power boot is another power-saving option where battery chemistry limits allowable peak currents. The L series allows the peripherals to operate autonomously in deep-sleep mode with an alternate-power source without involving the core or main system.

The ultra-low-power MCU Apollo 2 integrates up to 1MB flash with 256kB RAM to accommodate radio and sensor overhead. The ARM Cortex-M based processor has a power consumption of under 10µA/MHz. It is an improvement over Apollo 1, with current usage of about 35µA/MHz with sleep modes as low as 143nA.

MAX32630/MAX32631 from Maxim Integrated is another ARM Cortex-M based processor suitable for the wearable market. It has a power consumption of 106µA/MHz in 600nA low-power mode. It sits in the higher edge of low-power processors. Clocked in at 96MHz, the 32-bit processor sports 512kB SRAM with 2MB flash. An interesting part of the processor is the trust protection unit with encryption and security features. These features include a modular arithmetic accelerator for fast ECDSA, a hardware PRNG entropy generator and a secure boot loader.

But it is not just about reducing power.

As seen in MAX32630/1, removing encryption features could result in reduced power consumption, but the need for encryption is prime in today’s world. With every person holding multiple devices daily, securing data also becomes important. So a better fit, instead of just reducing power consumption, is to look at a scenario where the requirements are met with the lowest possible power.

Focus shifting towards power-performance balance

AMD Ryzen based on Zen architecture has been recently released. Apart from one processor model, it focuses on power-performance balance. So, the move towards extracting the most out of the processor seems to be well underway. Reducing power consumption comes at a price, and it can only be done until a certain point, post which the performance dips below expectations.

We will always look towards processors that consume low power to run more processes and allow extended battery life. Personally, getting an Intel or AMD processor to run off an AA battery would be the dream, but there is only so much that can be done.

For wearable devices, this is a whole different power struggle. With ARM Cortex M4 being the choice for major designs, future solutions should be interesting to look at. However, at present, balance between power consumption and performance looks to be the focus for processors of the future.

Feel interested check out other tech focus article.