This reference design is particularly useful in high-speed networking applications, data centers, and enterprise environments, where reliable and scalable connectivity is essential.

Gigabit Ethernet link aggregation is a crucial technology in modern networking, enabling higher bandwidth, improved redundancy, and enhanced network efficiency by combining multiple Ethernet links into a single logical connection. For design engineers, a Gigabit Ethernet link aggregator reference design serves as a valuable resource to streamline development, optimize performance, and ensure seamless data transmission. It provides a tested framework with hardware and software guidelines, reducing design complexities and accelerating time to market.

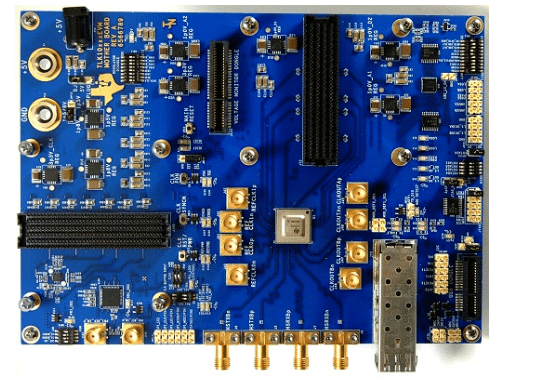

The Gigabit Ethernet Link Aggregator reference design TIDA-00269 by Texas Instruments (TI) features the TLK10081, a multi-rate link aggregator engineered for high-speed bi-directional point-to-point data transmission. By multiplexing lower-speed serial links into a single higher-speed link, this design significantly reduces the number of physical connections required, simplifying system implementation and management. The TLK10081 supports aggregation and de-aggregation of various serial links, including raw data formats, making it highly versatile for different applications.

To complement the TLK10081, this reference design incorporates the CDCM6208 device, which generates an extremely low-jitter clock input. This is particularly useful for systems that either lack an external clock source or fail to meet jitter requirements. The design ensures seamless evaluation of high-speed signals by routing channel A signals to SFP+ modules, which are commonly used in optical fiber systems. Meanwhile, channel B signals are routed to edge launch SMA connectors, facilitating easy testing using standard test equipment.

The TLK10081 supports various data types without specialized encoding, handling 1 GbE, SGMII, and raw data at 250 Mbps to 1.25 Gbps. It enables 8 × (0.25–1.25 Gbps) to 1 × (2–10 Gbps) multiplexing for efficient link aggregation. With flexible clocking, including externally jitter-cleaned clocks, it ensures signal integrity. Consuming just 800mW per channel, it is highly energy-efficient. Its aggregation of multiple serial signals into a single high-speed link reduces cable complexity, while de-aggregation ensures seamless data transmission.

This reference design is ideal for applications in both communications and industrial sectors. In communications, it can be used in optical network terminal units (ONTs) and WLAN/Wi-Fi access points. In industrial settings, it is suitable for air circuit breakers (ACBs), aircraft cockpit displays, digitizers (≥ 50MSPS), interconnect/distribution boxes, power analyzers, and programmable DC power supplies.

By utilizing the Gigabit Ethernet Link Aggregator reference design, customers can streamline their data transmission infrastructure, enhance system performance, and reduce hardware complexity. The combination of high-speed aggregation, flexible clocking, and low power consumption makes this solution a robust choice for high-speed networking and industrial applications.

TI has tested this reference design. It comes with a bill of materials (BOM), schematics, assembly drawing, printed circuit board (PCB) layout, and more. The company’s website has additional data about the reference design. To read more about this reference design, click here.