The multi-protocol subsystem IP delivers an impressive bandwidth density of 8 Tbps/mm and supports device-to-device data rates of 24 Gbps, catering to hyperscale, high-performance computing (HPC), and AI applications.

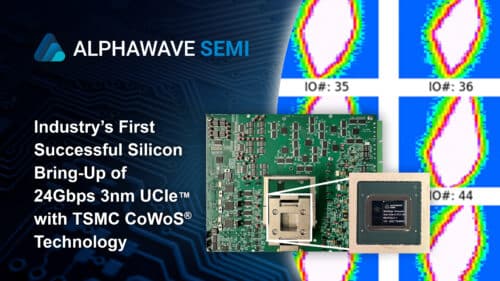

Alphawave Semi has introduced the industry’s first successful silicon bring-up of Universal Chiplet Interconnect Express (UCIe) Die-to-Die (D2D) IP at 3nm, utilising TSMC’s Chip-on-Wafer-on-Substrate (CoWoS) advanced packaging technology. The complete PHY and Controller subsystem, developed in partnership with TSMC, is aimed at applications such as hyperscalers, high-performance computing (HPC), and artificial intelligence (AI). Leveraging TSMC’s CoWoS 2.5D silicon-interposer-based packaging, this integrated and highly configurable subsystem delivers an impressive 8 Tbps/mm bandwidth density. It significantly reduces I/O complexity, power consumption, and latency.

The main features are:

- High Bandwidth Density and Data Rates

- Standard Package (2D) with 16-bit and 32-bit modules and Advanced Package (2.5D) with 32-bit and 64-bit modules

- Power-efficient, low-latency interconnect enabling connection between two dies via short-reach, low-loss channels.

- Robust Chiplet Ecosystem

The IP supports various protocols, including streaming, PCIe, CXL, AXI-4, AXI-S, CXS, and CHI, ensuring interoperability across the chiplet ecosystem. It also features live per-lane health monitoring for enhanced robustness and supports operation at 24 Gbps, meeting the high bandwidth demands for D2D connectivity. The UCIe subsystem IP adheres to the latest UCIe Specification Rev 1.1. It includes comprehensive testability and debug features such as JTAG, BIST, DFT, and Known Good Die (KGD) capabilities, ensuring reliable performance and ease of integration.

“Achieving successful silicon bring-up of the 3nm 24 Gbps UCIe subsystem with TSMC’s advanced packaging is a significant milestone for Alphawave Semi. It underscores our expertise in leveraging the TSMC 3DFabric™ ecosystem to deliver top-tier connectivity solutions,” said Mohit Gupta, Alphawave Semi’s SVP and GM of Custom Silicon and IP. He also emphasized that this IP sets “a new benchmark in high-performance connectivity solutions.”