Compatible with most of the existing PCS standard definitions and based on an innovative self-tuning architecture

MosChip Technologies Limited, a semiconductor and system design services company has unveiled a multi-protocol Long Range (LR) 8G SerDes PHY in 28nm. It is part of MosChips’ high-performance multi-rate transceiver portfolio, meeting the growing needs for small footprint, low-power consumption and low latency edge applications.

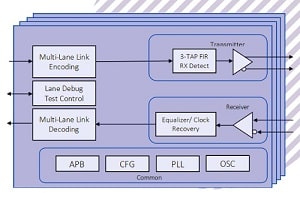

“Our LR 8G PHY is implemented as a self-contained protocol-agnostic Physical Medium Attachment (PMA) IP with a flexible digital I/F on the system side that could be made compatible with most PCS standard definitions that exist in the industry today,” said Albert Vareljian, Chief Architect at MosChip. “ PHY is based on our innovative self-tuning architecture and fully adaptive continuous-time equaliser with automatic gain control analogue front end (AFE) combined with adaptive multi-tap decision feedback equalisation (DFE) to cover channel variations and PVT range”.

PHY is fully configurable for programmable lane enable/disable and choices of macros pre-configured for 1 to 16 lanes and supports various debug features such as serial and parallel loop back. The 8G PHY macro is backwards compatible and can operate in compliance with PCI Gen1/2, SATA 1/2 specifications. It includes a PCIe standard multi-lane interface. No external passive components are required, saving area at the system level and pin count at the chip level.

“This is a major milestone for MosChip, which highlights our strategic focus to develop niche SerDes PHY IP that is customisable as per customer end applications,” said Venkata Simhadri, MD/ CEO of MosChip. With the addition of silicon-proven LR 8G PHY to our portfolio, we are well-positioned to provide both custom/porting PHY IP services and turn-key mixed-signal ASIC solutions.

LR 8G PHY macro deliverables include a complete set of logical views, physical views, documentation, Verilog model, a UVM-based verification environment, an abstract view, liberty files, netlist, GDSII and flip-chip bump/ball map plans.