Use composite measurements, reduce measurement time

In order to reduce measurement time, “The idea is to perform composite measurements instead of configuring each measurement separately. Because composite measurements calculate multiple measurement results on a single burst, they are more efficient than when each measurement is performed sequentially. Multicore processors enable this to be done in parallel, resulting in a faster overall test time when using a software-defined approach,” suggests Tarun Gupta, business development manager at National Instruments.

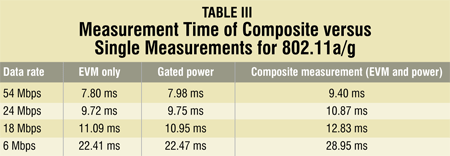

Consider the case of measuring both power and error-vector magnitude (EVM) of a WLAN transmitter. Typical measurement times for these individual measurements are listed in Table III. In this case, each 802.11a/g EVM measurement is calculated using 16 OFDM symbols. The gated power measurement is performed on the portion of the burst from 20 to 120 µs.

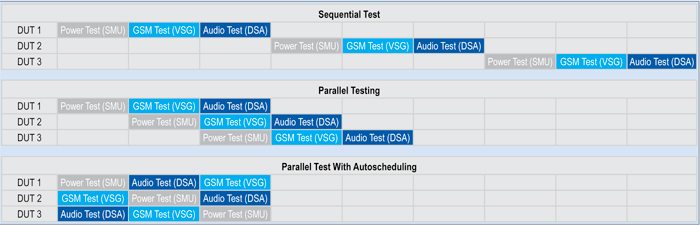

[stextbox id=”info” caption=”An example: Testing smartphones”]Assume that you are testing smartphones and running three different tests on each: a power consumption test that uses a programmable source measure unit (SMU), a GSM test that uses an RF vector signal generator (VSG) and an audio quality test that uses a dynamic signal analyser (DSA). Assume that each of these tests takes one unit of time to execute. On a typical test system that tests one phone at a time sequentially, you would test these phones at a rate of one device under test (DUT) every three units of time. Testing three phones would take nine (3×3 = 9) units of time.

The sequential test example in Fig. 2 shows that each test instrument is left unused for six of nine time units. That’s a 66 per cent downtime per instrument! Imagine how much more efficient your test system could be if you use this downtime to start testing the next phone. This is precisely what you can do with parallel testing.

[/stextbox]

Table III shows that when you perform key 802.11a/g measurements such as EVM and power as a composite measurement on a single burst, the total measurement time is significantly lesser than the sum of each individual measurement time.

Table III shows that when you perform key 802.11a/g measurements such as EVM and power as a composite measurement on a single burst, the total measurement time is significantly lesser than the sum of each individual measurement time.

Ensure upgradability, optimise time and investments

Being smart during the initial phase of chipset design can go a long way to reduce the pain of any change to be made on the hardware at later stages. By using readymade libraries in the design or simulation software, a designer can optimise the time at the initial stages itself.

Sadaf Arif Siddiqui, technical marketing specialist, Agilent Technologies, explains how the W1917EP WLAN baseband verification library helps in this respect. “The W1917EP WLAN baseband verification library is a new Layer 1 simulation reference library for Agilent SystemVue. The blockset, reference designs and test-benches of the W1917 assist the design and verification of multi-format radios, by providing configurable physical-layer waveforms for networking standards 802.11a and 802.11ac,” he says.

A new breed of spectrum analysers is now available that provides a different approach to signal analysis. For instance, X-Series spectrum analysers are able to run MATLAB and 89600 VSA software inside the analyser itself. Moreover, it provides a library of measurement applications that can be used with the spectrum analyser. For instance, one such measurement application enables the X-Series signal analysers to emulate the FSP/FSU/FSE spectrum analysers or ESU EMI receiver in remotely controlled, automated test equipment systems. Another application in the same library enables users to check the electromagnetic interference by running pre-compliance radiated and conducted emissions tests for both commercial and military standards.

As all these applications are available from a single point, they help test engineers to achieve measurement integrity and drive productivity.

Get started

Now that you have got an idea about the numerous factors that can optimise your test system, you can put these to use. You could also devise your own tweaks to get more performance out of your system by balancing trade-offs.

The author is tech correspondent at EFY Bengaluru