Heterogeneous computing. Automated test systems have always comprised multiple types of instruments, each best suited for different measurement tasks. An oscilloscope, for example, can make a single DC voltage-level measurement, but a digital multimeter provides better accuracy and resolution. It is this mix of different instrumentation that enables tests to be conducted in the most efficient and cost-effective manner possible. The same trend is now affecting how engineers implement computation in test systems. Applications such as RF spectrum monitoring, for example, require inline, custom signal processing and analysis not possible using a standard PC CPU.

Furthermore, test systems are generating an unprecedented amount of data that can no longer be analysed using a single processing unit. To address these needs, engineers have to turn to heterogeneous computing architectures to distribute processing and analysis.

IP to the pin. For decades, the electronics industry has pursued its version of the holy grail—concurrent design and test. Many have believed this to be an unattainable goal, considering how far apart the two worlds appear. In the design world, most engineers design at a system level using the latest electronic design automation (EDA) software, which has seen tremendous innovation over the last decade. The test industry has, however, not innovated as quickly, and many companies have chosen to invest more in their design tools than their test engineering tools. The consequence is test engineers are typically outmatched when testing the latest software-centric electronic devices.

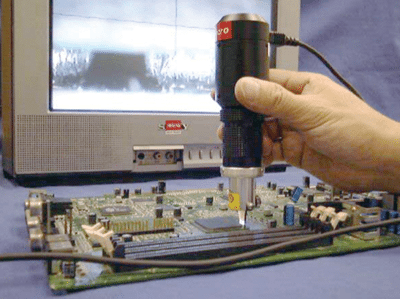

The next phase in integrating design and test is the ability for engineers to deploy design building blocks, known as intellectual property (IP) cores, to both the device under test (DUT) and the reconfigurable instrument. This capability is called ‘IP to the pin’ because it drives user-defined software IP as close to the input/output (I/O) pins of next-generation reconfigurable instruments as possible. The software IP includes functions/algorithms such as control logic, data acquisition, generation, digital protocols, encryption, math, RF and signal processing.

Strategies to lower the test cost

A functional test platform can lower the cost of manufacturing test in three key ways: By increasing the test system throughput, increasing the engineering productivity and lowering the overall cost of ownership.

Increasing the test system’s throughput. Increasing the throughput is a goal of every high-volume manufacturer. In many manufacturing lines, functional test cannot keep up with the beat rate of devices coming out of production. Because it is usually highly undesirable to slow down the production process to accommodate test, the most common solution is to have multiple functional testers at the end of each line to keep up with the production throughput. This condition is commonly called test fan-out. As this proliferation of test equipment can be avoided by reduced test times, lower capital equipment expenditures can be achieved.

The PCI eXtension for instrumentation (PXI) platform provides tremendous performance advantages over other hardware platforms. Built on the industry-standard PCI bus, it offers data throughput of up to 132 MB—more than a hundred times faster than the throughput of a general-purpose interface bus (GPIB) device. This high data throughput means that measurement data can be quickly transferred from the measurement device to the computer where a decision can be made or data can be logged and thus the test time for the device be significantly reduced.

To further increase the throughput, PXI provides star-triggering capability. With the star trigger, several PXI devices can be tightly synchronised on common trigger or clock signals. In many applications, the use of the star trigger has resulted in throughput gains of ten times or more.

The Interchangeable Virtual Instrument (IVI) standard for instrument drivers provides a state-caching driver model to eliminate redundant calls to instrumentation and significantly increase performance. IVI instrument drivers can deliver performance gains of ten times or more over traditional drivers without state-caching technology.

To deal with fan-out at functional test, many manufacturers place several independent but identical testers in parallel. However, this method uses capital equipment very inefficiently, because even under-used instruments are duplicated for each tester. A far more efficient method is to test several devices in parallel on a single, parallel tester with multiple test sockets. A parallel test strategy offers the most efficient use of equipment because more expensive, under-used instruments can be shared among sockets while more common instrumentation can be duplicated per socket for maximum throughput.

Increasing the engineering productivity. Getting a product into volume production and on the market as soon as possible can make the difference between a successful product and a failure. In highly competitive industries, for example, a six-month delay in the shipment of a product can result in more than a 30 per cent decrease in cumulative profits over the entire life-cycle of the product. For such applications, developing a manufacturing test system rapidly is essential, as is quickly adapting a tester after product revisions.