DECEMBER 2012: On an average, a chip holds over one billion transistors today. Intel’s 10-core Xeon Westmere-EX packs 2.6 billion transistors into a 512mm2 area using 32nm technology. But even that is not enough. The thirst for more features and processing power is unquench-able, but how much more can you pack into a chip? If transistors get any smaller, their reliability could become questionable. Plus, if you need to make chips denser, the fabrication costs might also become unreasonably high.

Such issues have led to the adoption of three-dimensional (3D) integrated circuit technology, wherein two or more dice are stacked atop each other and linked with suitable interconnects. You can draw a parallel with skyscrapers, which help overcome space shortage within large cities, and elevators that make it possible for people and even vehicles to easily travel to any of the floors.

What are the main benefits of 3D chips?

1. 3D chips save space. Dice that used to be centimetres apart on a chip can now be placed millimetres apart, and that too vertically.

2. Since the dice are close by, the interconnect length is significantly smaller. This results in low latency and higher performance.

3. Stacking helps overcome the memory-to-processor performance bottleneck that plagues 2D ICs.

4. 3D interconnects permit data to be moved both horizontally and vertically. This helps boost performance by 30 to 40 per cent.

5. Bandwidth is much higher as it is possible to have a large number of vertical vias between the layers. Moreover, interconnects between dice in the 3D IC do not use input/output (I/O) buffers or bond wires.

6. 3D chips consume 40 to 50 percent less power than traditional ICs.

7. 3D stacking permits heterogeneity, since the dice arranged one above the other need not be similar. This allows a designer to optimise components according to their function.

Are today’s ‘3D’ chips really 3D?

There is a difference between a 3D package and a 3D IC.

In a 3D package, separate chips are stacked in a single package. They may be stacked one above the other or side-by-side. This arrangement is often called a chip stack, system-in-package (SiP) or multi-chip module (MCM). Here the chips are merely stacked and connected using interconnects but not integrated into a single chip.

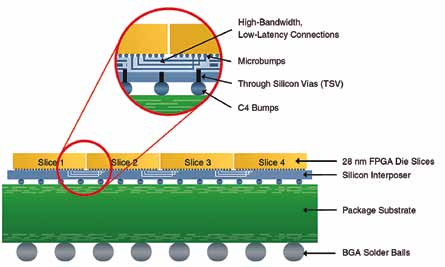

In contrast, a 3D IC is a single chip. Multiple dice are stacked, connected using through-silicon vias (TSVs), and multiple groups of dice again connected together using a silicon interposer—and all of this is mounted on a single SiP.

3D chips are in development stage, and any chip touted as 3D today is essentially a 2.5D chip or a 3D package as most of the commercially-available or practicable designs today are MCMs or package-on-package. Pure 3D ICs (stacking in package) are still a point of research in most companies, and the big foundries have just figured out the processes and interposer technology for the same.

Although Intel has showcased quite a few 3D ICs in the past, such as the 3D Pentium CPU in 2004 and the Teraflops Research Chip in 2007, the area continues to haunt the silicon giant because of the difficulty in heat dissipation and the high cost of manufacturing involved. This year too, 3D-IC-based multi-core designs using GlobalFoundries’ 130nm process and Tezzazon’s FaStack technology were demonstrated at a leading conference, as also some designs by teams from the Georgia Institute of Technology and the University of Michigan. However, it is unclear when the technology might actually reach production.

Techniques for stacking the dice in a 3D chip

There are several ways to stack chips. Giles Peckham, EMEA director-Marketing, Xilinx, explains the most common ones:

1. Connecting two stacked chips to a flip chip at the bottom of the stack. Examples are SoCs where dynamic random-access memory (DRAM) is placed on top of the central processing unit (CPU).

2. Using TSV, where the dice are placed on top of each other and connected through vertical copper channels. An example of TSV usage is the super-density DRAMs used in camera CMOS sensors.

3. Making use of a silicon transposer, which connects two or more chips together—much like the transposers used in AMD graphics cards.

Xilinx adopts a technology called stacked silicon interconnect (SSI). In this architecture, multiple dice are placed side-by-side on top of a passive silicon interposer, which facilitates interconnect/communication between the many dice. Such a design, where the chips are placed side by side, is called a multi-chip module but should not be confused with a traditional MCM in which the connections between the chips are made via powerful I/O buffers and bond wires. In SSI technology, the connections are virtually seamless, the interposer being an extension of the on-chip interconnect with microbumps to join them. With more than 10,000 interconnects that can be programmed among the dice, and programmability of each die and the I/O, the company claims its ICs to be one of the first commercially-available, completely-programmable 3D ICs.