The difference between a latch and a flip-flop in digital electronics is that a latch is level-triggered (outputs can change as soon as the inputs change) and a Flip-Flop is edge-triggered (only changes state when a control signal goes from high to low or low to high).

Latches are something in your design that always needs attention. Some tools help designers pinpoint the existence of latches in their design as ‘must know’ information.

Then, it is the designer’s responsibility to correct if the latch usage is unintentional, as this could easily have happened due to poor RTL coding practices.

Once the latch existence is acknowledged at the synthesis level, then the downstream tools follow those conventions. This statement is suitable for ASICs, but latch existence is not acceptable for FPGAs.

It would be fine to say that FPGA tools have more accurate timing analysis for flop-based designs.

You can check the difference between FPGA and ASIC if interested.

An expert designer knows how to utilize the time-borrowing capability of a latch for slack balancing while optimizing latch-based critical paths in the design.

Once he or she decides to use latches in a particular design, the engineer has to make sure that the enabled signal is stable and valid data is being captured in the latch. This helps to avoid unstable states in the design.

Let’s go through the latch vs flip-flop comparison and try to understand which is better than the other.

Difference between Latch and Flip Flop

| Latch | Flip-Flop |

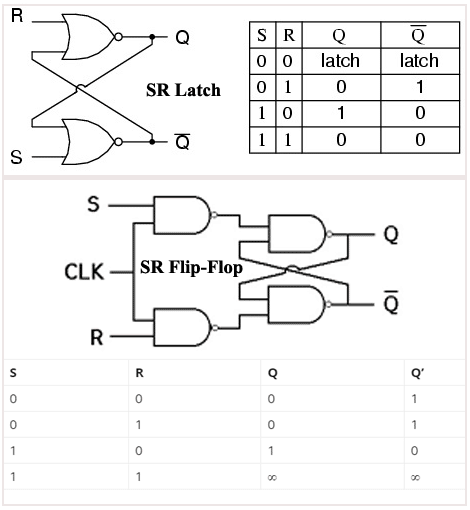

| The latch is transparent – because the input is directly connected to the output when enable is high. It means Latch is sensitive to pulse duration (also called soft barrier) | Flip-flop is a pair of latches (master and slave flop). Flip-flop is sensitive to pulse transition. The signal only propagates through on the rising/falling edge (also called hard barrier) |

| Less Area (less gates) | More Area (more gates) because the flip-flop contains two latches. |

| Less Power (less gates) | More Power (more gates) |

| Fast – (The longer combinational path can be compensated by shorter path delays in the subsequent logic stages. That’s why, for higher performance, circuits designer are turning to latched-based design.) | Slow – (The delay of a combinational logic path of a design using edge-triggered flip-flops is always less than the clock period except for those specified as false paths and multiple-cycle paths. Hence the longest path of a design limits the circuit performance.) |

| Require more tool manipulation and more hand calculations to verify that they meet the timing | Easy to check design timing using Static Timing Analysis (STA) tools |

| Cycle-borrowing to gain more setup time on the next register stage, as long as each loop completes in one cycleTo meet the timing in the design, Designers consider latches to adjust timing mismatch. | Data launches on one rising edge, so it must be set up before the next rising edge. If it arrives late, the system fails. If it arrives early, time is wasted due to hard edges in Flops |

| For ASICs with large clock skew, latches have substantial benefits for reducing the clock period | Even for the high-speed pulsed flip-flops with zero setup time, as they are not transparent, the impact of the clock skew is not reduced |

| Level-sensitive latches reduce the impact of the inaccuracy of wire load models and process variation. | Flip-flops demand the highly accurate wire load model and process |

| In DFT, Latches are needed as a lockup state at the clock domain crossings in the scan chain to avoid unpredictable behaviour | In DFT, use flops that can be scanned (controllable and observable) |

| In FPGA, level-sensitive transparent latches should be avoided in FPGAs | In FPGA, edge-sensitive flip-flops are used exclusively. Timings analysis is more appropriate with flops for FPGA tools |

| Circuit analysis is complex. You may see last minutes timing mismatch surprises at the implantation stage. | Circuit analysis is easy |

| High-speed microprocessor designs typically use master-slave latches instead of flip-flops so that logic can be added between the rising and falling clock edges.Most of these companies have written their own specialized STA tools to verify latch-based designs. | The most commonly used flop in the design world is D type flip-flop.FSM implementation mostly involves D Flip-flops due to a minimum number of logic gates and lesser cost as compared to other types of flip-flops. |

| For non-timing-critical configuration registers, latches work great, due to fewer gates and less power consumption | For non-power aware design, Flip flops are preferred over Latches |

| The latch is an asynchronous block. Therefore you must ensure that the combinational functions, which generate input signals for the latch, are race-free. Otherwise, they may generate glitches, which may be latched, causing hazards in your system. | A flip-flop, on the other hand, is edge-triggered and only changes state when a control signal goes from high to low or low to high |

| Latch-based design is noisy because any noise in the enable signal disrupts the latch output easily. | Flip-flop-based design is robust |

Now we can say that latch is not that bad and quietly useful in specific applications.

Comment down below what you think…

About the Author…

Arbind is a Core Competence Applications Engineer with Atrenta. He has eight years of experience in VLSI design specializing in RTL checking and optimization. Arbind has an M.Tech in VLSI Design from IP University, New Delhi. Arbind has authored many technical papers and articles on different topics for various conferences and publications. Email: [email protected]

Nice and well-elaborated article

Thank you for your feedback.

contain information really sought at single place.

Thank you for your feedback.

thanks very much for your electronics projects .

Thank you for your feedback.

Good article .

Thanks for sharing this valuable information .

Thank you for your feedback.

Wonderful article on latches and flipflops..

Thank you for your feedback.

Could you please explain brief on why latch is faster than flip flop

Because it doesn’t need any clock signal

Latch transparency between input and output makes faster compared to Flip Flop which has master-Slave (consists of two latches) and one is transparent at a time.

Well elaborate the both. Thanks.

Great article

I cleared all my doubt..

Thank you for your feedback.

very good compile

lovely information

Thank you for your valuable feedback.