P channel Enhancement MOSFET is a 3-terminal device. Let us first take a look at its construction followed by the working principle and VI characteristics.

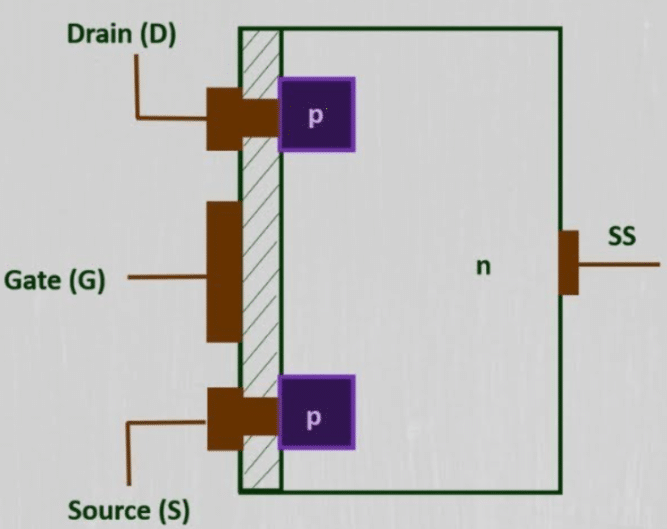

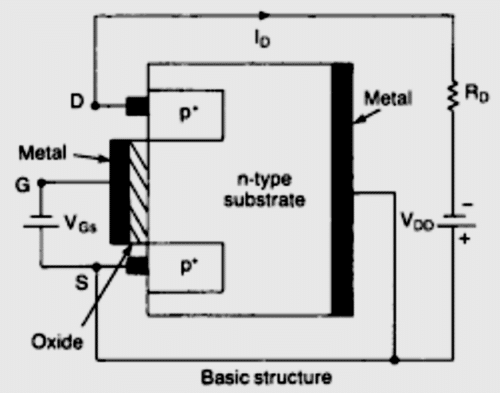

The body of any P-channel MOSFET is made up of N-type material. 2 P-type materials are diffused at the top. A depletion region will be formed in the PN junction. A metal contact is made at the bottom of the N-type substrate and a terminal is taken out called the body or substrate.

Also Read: Everything you need to know about MOSFET

Similarly, a metal contact is made at the top of both the P-type materials, and two terminals are taken out as Drain and source. A Silicon dioxide layer is drawn in between the two P-type wells at the top. A metal contact is made at the top of it and a terminal is taken out called a Gate terminal. You can see it is a 4-terminal device. But we earlier said that it is a 3-terminal device.

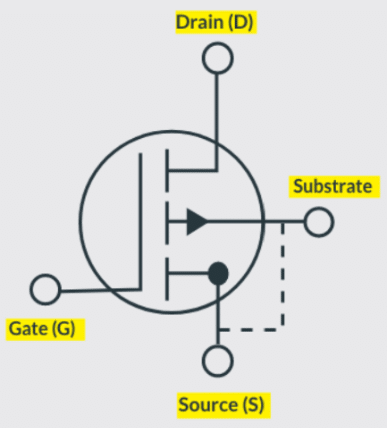

Now, what happens is generally the body terminal and source terminal are internally shorted and connected to the ground. Hence now only three terminals are visible namely Source, Drain, and Gate.

P channel enhancement MOSFET is similar to N channel enhancement MOSFET, the only difference is in the polarities of applied voltages.

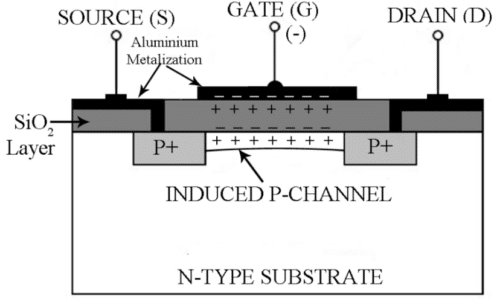

To get the drain current first we have to create a channel for the free movement of holes. To create a channel we have to apply a voltage between the gate and source terminal keeping Gate at a lower potential. This voltage is called VGS. Now the gate is at a lower potential. The free holes will move toward the gate terminal. As discussed earlier we have a Silicon Dioxide layer at the top.

Hence these free holes will accumulate near the Gate region and will not escape. The silicon dioxide layer also acts as a dielectric. It will allow more free holes to accumulate near the gate terminal in less applied voltage at the gate terminal.

Now on increasing the negative value of VGS further, a high electric field is developed forcing atoms inside the N substrate to break. The free electrons generated will fill the electrons near the gate region. This way electrons are pushed away from the gate terminal increasing P-type behavior near the gate terminal. A time will come when a P-channel is created between the two P wells. The VGS voltage at which the channel is created is called the threshold voltage or VT.

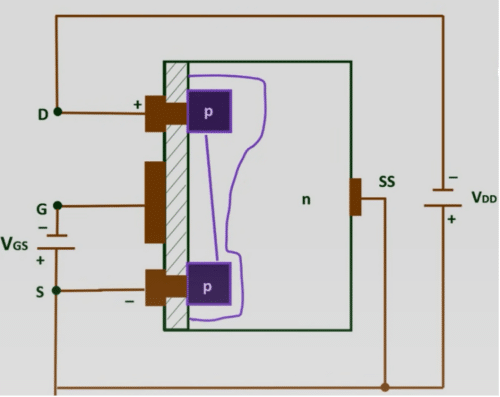

We can conclude from this discussion, when |VGS| > |VT| a P channel is induced near the gate terminal as shown in the figure below.

A channel is created still we are not getting any current. Let us see how to get the drain current. Apply a voltage source between the drain and the source keeping the drain at a lower potential. This voltage is called VDS. On applying this voltage, the drain current or ID will start flowing.

We can conclude from this discussion, when |VGS| > |VT| and VDS < 0, the current ID flows from drain to source as shown in the figure below.

On increasing the negative value of VDS further ID will increase. But will this ID keep on increasing with VDS?

The answer to this question is no. On increasing the negative voltage at the drain terminal, a reverse bias is formed at the PN junction near the drain terminal. This will result in a thick depletion region near the PN junction.

Hence on increasing the negative value of VDS further you will see the channel near the drain terminal is becoming narrow. The drain current will face more resistance near the drain terminal. A situation will reach when the drain current becomes constant and will not increase further.

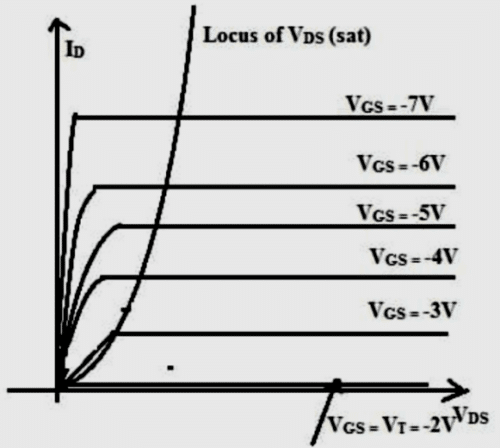

This situation is called the pinch-off situation and the drain current is called the saturation current. The voltage at which we will get saturation current is called saturation voltage.

We can conclude from this discussion that pinch-off is reached when VGS < 0 (constant) and VDS = VDS(SAT), ID = ID(SAT) as shown in the figure below.

Now is there any way to increase the drain current beyond saturation?

The answer is yes. Increasing ID further increases the negative value of VGS. This will increase the width of the complete P-channel. Hence VGS is controlling voltage. Now we can plot VI characteristics very easily.

In the VI characteristics, you will see the plots of |VDS| vs |ID| for various values of |VGS|.

From the graph, it is clear that the current ID will become constant at a specific value of VDS. current ID increases only when the negative value of VGS is increased.